本系列主要介绍视频编解码芯片的设计,以HEVC视频编码标准为基础,简要介绍编解码芯片的整体硬件架构设计以及各核心模块的算法优化与硬件流水线设计。

本文将首先介绍HEVC标准中,分像素运动估计的亮度分量和色度分量的插值方法,以及HM中分像素运动估计的搜索方法。然后,我们提出了一种基于4步搜索策略的分像素运动估计算法和粗略运动向量预测CMVP方法,并进行了对应的FME硬件架构设计和VLSI实现。最后,我们对所提出的FME架构进行了测试,展示了包括硬件面积和编码速度在内的指标结果。

概述

自然场景中的图像一般是模拟和连续的,图像中物体的运动也是连续的。因此运动的偏移也不会是整数像素的跳跃式运动。因此为了提高预测的准确性,分像素精度的运动估计被引入到视频压缩编码技术中。

1

插值计算

通过各种方式采样到的视频,本身并不包含分像素。分像素须由整像素经过一定的插值计算才能够得到。因此在整像素运动估计和分像素运动估计之间,需要在参考帧图像的搜索范围内进行分像素点的插值计算。

图1

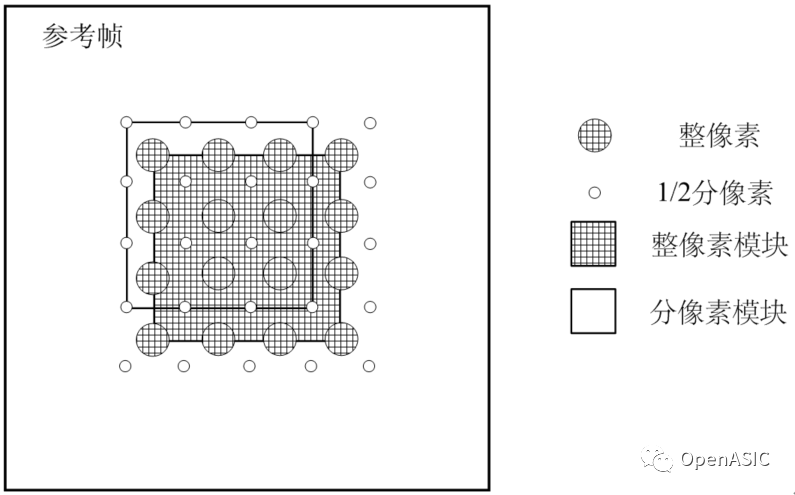

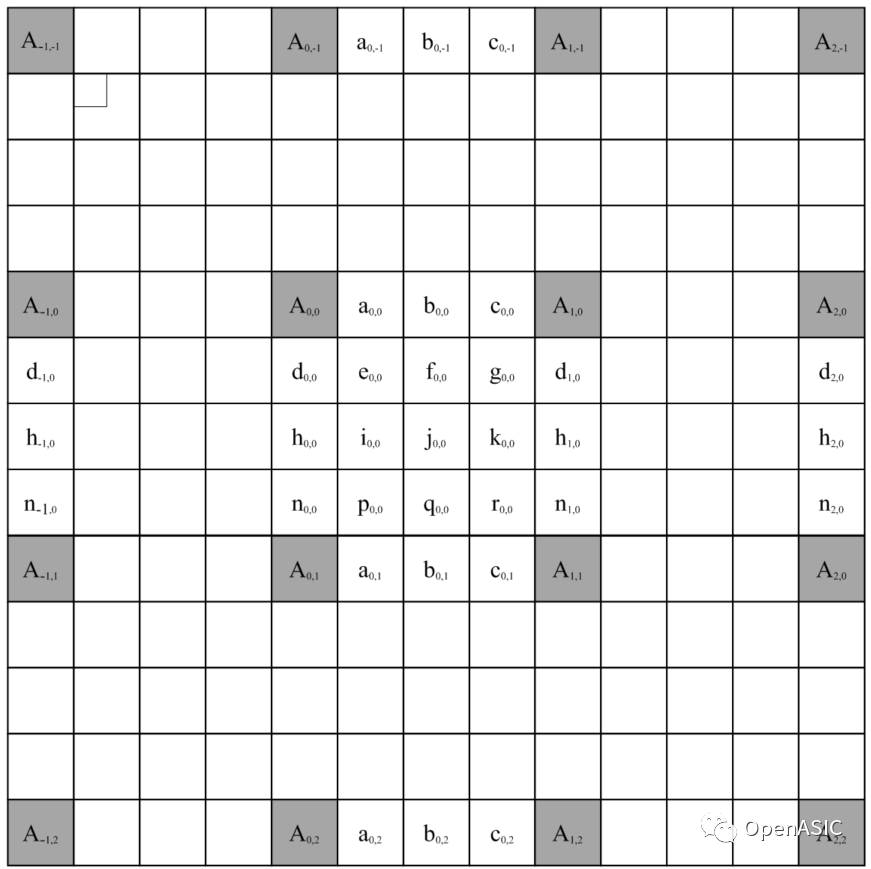

与H.264/AVC编码标准类似,在H.265/HEVC标准中,对于视频序列的亮度(Luma)分量,其分像素运动估计的精度为1/4个像素;相应的,对于YUV 4:2:0视频序列的色度(Chroma)分量,其分像素运动估计的精度为1/8个像素。但是,相较于H.264/AVC中使用的6抽头滤波器(用于1/2像素插值)和2抽头滤波器(用于1/4像素插值),H.265/HEVC使用了更多的邻近像素用于插值:在1/2亮度像素的插值过程中,HEVC采用了8抽头滤波器,而在1/4和3/4亮度像素的插值过程中,HEVC采用了7抽头滤波器;在色度像素的插值过程中,HEVC采用了4抽头滤波器。亮度插值的对应位置如下图2所示,其中a和d是1/4精度像素插值位置,b和h是1/2精度像素,c和n是3/4插值位置的像素。

图2

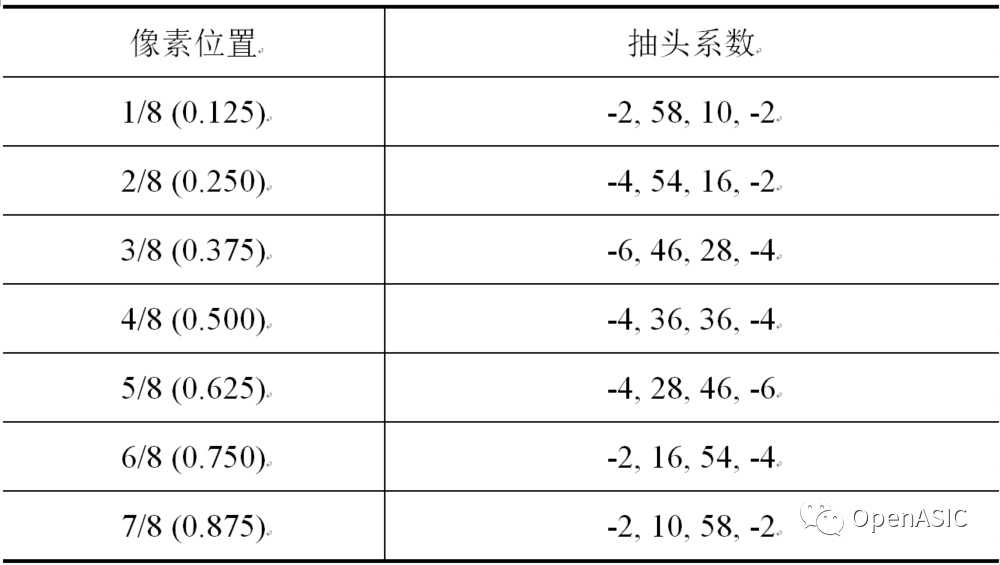

图中深灰色的部分是整像素运动估计完成后的整像素点,首先就需要依据这些整像素点进行插值。不同位置的分像素所用插值滤波器的系数不同,如下表1所示。

表1

可以发现,分像素位置分为两种,一种是与整像素点位于同行或者同列的分像素,另一种则是不与整像素同行或者同列的分像素。因此针对这两种不同的分像素,可分为两步对它们进行分别插值。

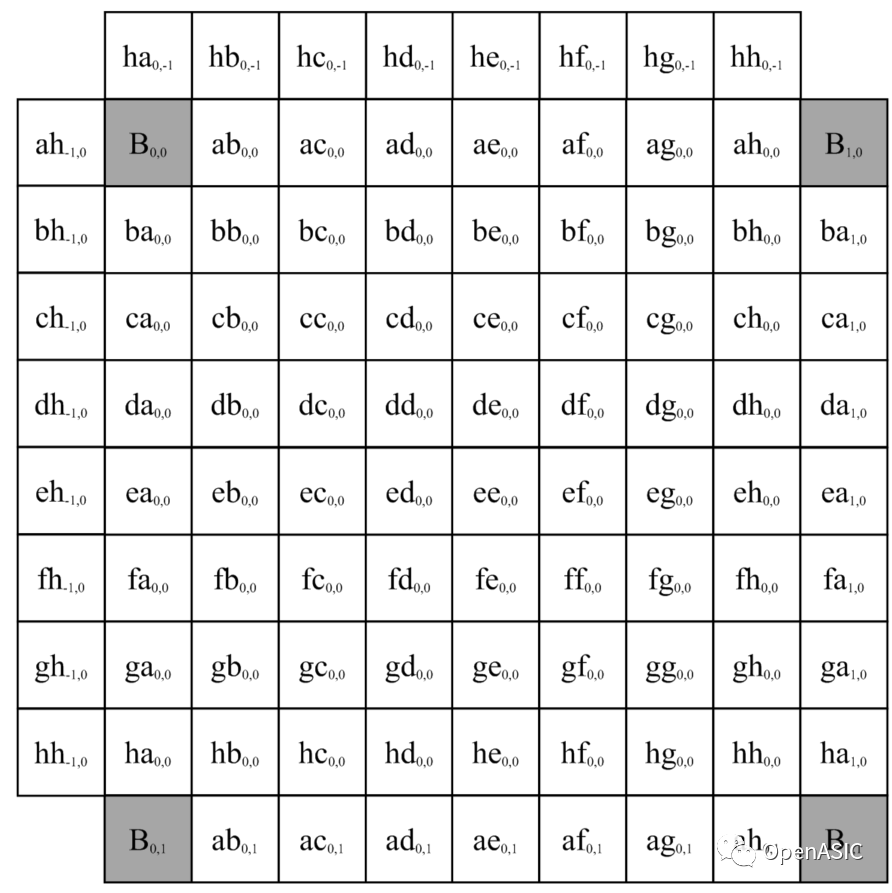

亮度分像素的插值完成后,就要进行色度分像素的插值。色度分像素的插值精度是1/8,因此需要插值的像素会更多,具体位置如下图3所示。

图3

与亮度分像素的插值十分类似,色度分像素插值也是分为两步。首先对与整像素点同行同列的分像素点进行插值,然后对其余剩下的分像素点进行插值。色度分像素插值滤波器系数如下表2所示。

表2

HM中的搜索过程

HM中分像素运动估计采用了两步搜索法:

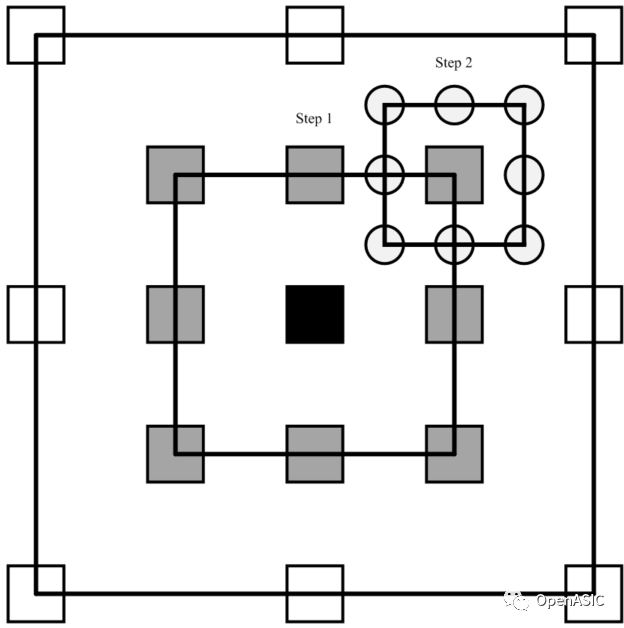

(1) 以整像素运动估计搜索出来的最佳整像素运动矢量为中心,得到其附近的8个1/2像素点,并插值得到这8个1/2像素点对应的亚像素参考块。计算这9个点(8个1/2像素点和1个整像素点)的代价,取代价最小的点作为第1步的最佳亚像素运动矢量。

(2) 以第1步的最佳亚像素运动矢量为中心,得到其附近的8个1/4像素点,并插值得到这8个1/4像素点对应的亚像素参考块。计算这9个点(8个1/4像素点和1个1/2像素点)的代价,取代价最小的点作为最终的最佳亚像素运动矢量。

图4

运动向量预测

HEVC标准提出了Merge模式和AMVP模式,以达到节约编码比特数、提高编码效率的目的。

在Merge模式下,利用已编码PU的运动信息为当前PU建立一个候选运动矢量集,其中包含5个候选运动矢量,对其进行遍历,选择其中率失真代价最小的一个直接作为当前PU的MV,以此代替当前PU的运动估计过程。这样大大降低了计算量,且当前PU的MV等于空域或时域上相邻块的MV,则不存在MVD,大幅省去了编码MVD的比特数。

高级运动向量预测(Advanced Motion Vector Prediction,AMVP)是H.265/HEVC标准提出的一项技术,其基本原理是对于当前正在搜索的预测单元PU,利用其时域和空域邻近块的运动矢量,为其建立一个候选预测矢量列表,包含两个预测运动矢量MVP[0]和MVP[1]。编码器从其中选择最优的MVP,传递给运动估计的模块作为其搜索的起点;运动估计完成后,得到MV与该MVP的值会非常接近,那么计算出的MVD就会较小,用对MVD进行编码代替对MV编码,需要的比特数将大大减少,由此来提升编码效率。解码端会建立同样的MVP列表,再结合码流中读取的MVD信息,即可恢复出MV。

算法优化

搜索方法

在本文提出的分像素运动估计的算法中,我们采用了4步搜索策略:

(1) 以整像素运动估计搜索出来的最佳整像素运动矢量为中心,得到其附近的8个1/2像素候选点,并插值得到这8个1/2像素候选点对应的分像素参考块。计算这9个候选点(8个1/2像素候选点和1个整像素候选点)的代价,取代价最小的候选点作为第1步的最佳亚像素运动矢量。

(2) 以粗略运动向量预测得到的MVPA(见下图)为中心,得到其附近的距离为1/4像素的8个候选点,并插值得到这9个候选点(8个周边候选点和1个MVPA像素点)对应的参考块。计算这9个候选点的代价,取代价最小的候选点作为第2步的最佳运动矢量。

(3) 以粗略运动向量预测得到的MVPB(见下图)为中心,得到其附近的距离为1/4像素的8个候选点,并插值得到这9个候选点(8个周边候选点和1个MVPB像素点)对应的参考块。计算这9个候选点的代价,取代价最小的候选点作为第3步的最佳运动矢量。

(4) 比较第1步、第2步和第3步的最小代价,得到最终的最佳运动矢量。

图5

我们提出的搜索算法检查了个搜索点,比Lin Y[1](6个)、Chen Y[3](25个)和He G[4](12个)工作中搜索点数目都要更多。此外,该搜索算法除了检查了最佳整像素运动矢量附近的亚像素搜索点,还检查了两个粗略预测矢量附近的搜索点,也就是说,该算法覆盖的范围更广。

在第2步和第3步中,由于MVPA和MVPB不一定是整像素运动矢量,因此其周围8个候选点可能为整像素候选点,也有可能是1/2亚像素搜索点或者1/4亚像素搜索点。在本节搜索算法对应的硬件设计中,1/4亚像素搜索点对应的参考块并不依赖于1/2亚像素搜索点的插值结果。我们的设计会增加插值模块的硬件代价,但也因此能够支持9个候选点的同时搜索。

粗略运动向量预测

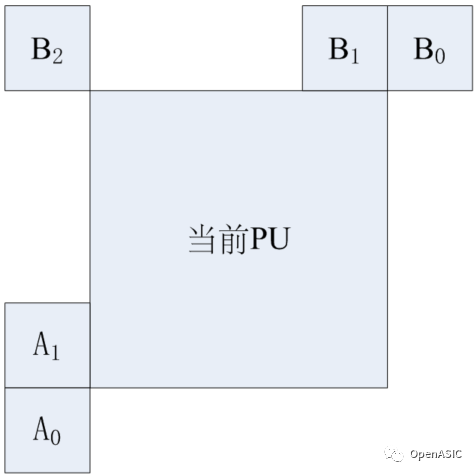

在分像素运动估计的代价估计阶段,我们采用了残差的SATD变换值和MVD的代价之和作为评判标准。但是,在我们的HEVC编码器硬件设计中,LCU的块划分模式在FME后续的RDO阶段才能获得,所以FME阶段没法得到精确的AMVP结果。因此,我们提出了粗略运动向量预测方法(Coarse Motion Vector Prediction,CMVP),其基本原理是不考虑LCU的划分,对于每个PU,其预测矢量为对应位置的8×8块的最佳运动矢量。

图6

如上图6所示,黑色线代表了最终RDO计算得到的块划分模式。对于16×16大小的PU块,其AMVP得到的A0矢量应该是图中红色线16×16块的最佳运动矢量;在本设计的FME中,通过CMVP得到的A0矢量是图中黄色线8×8块的最佳运动矢量。考虑到黄色线8×8块属于红色线16×16块,我们通过该黄色线8×8块得到的最佳运动矢量应该近似于AMVP中A0矢量的大小。

VLSI实现

硬件设计架构

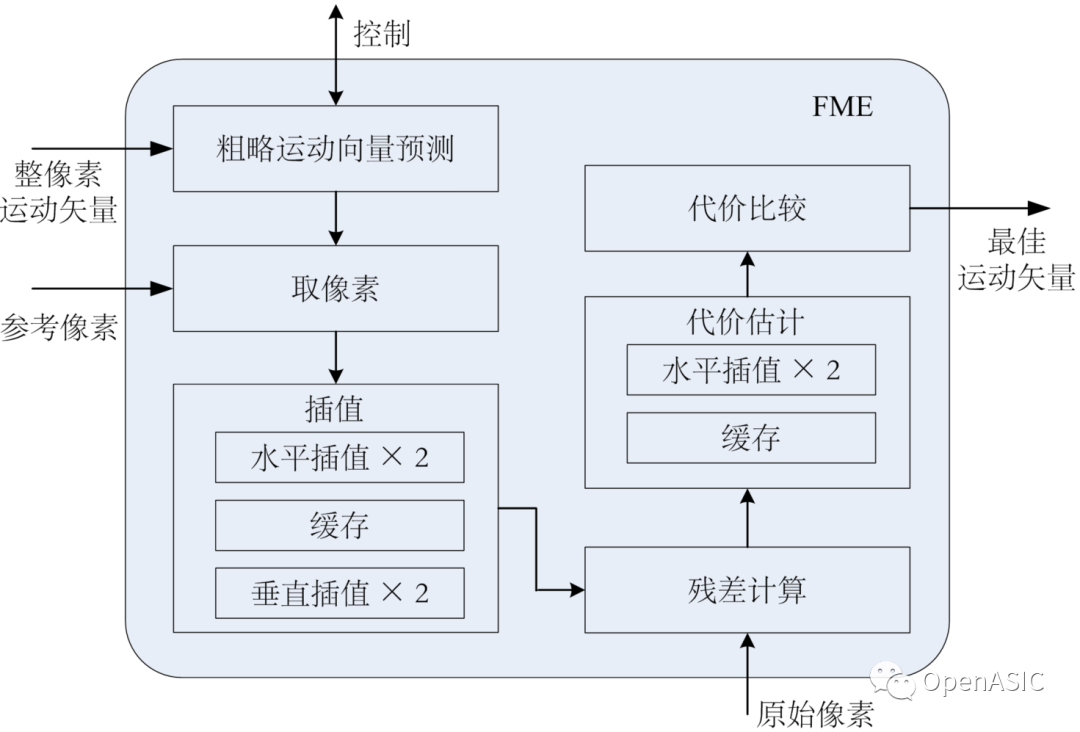

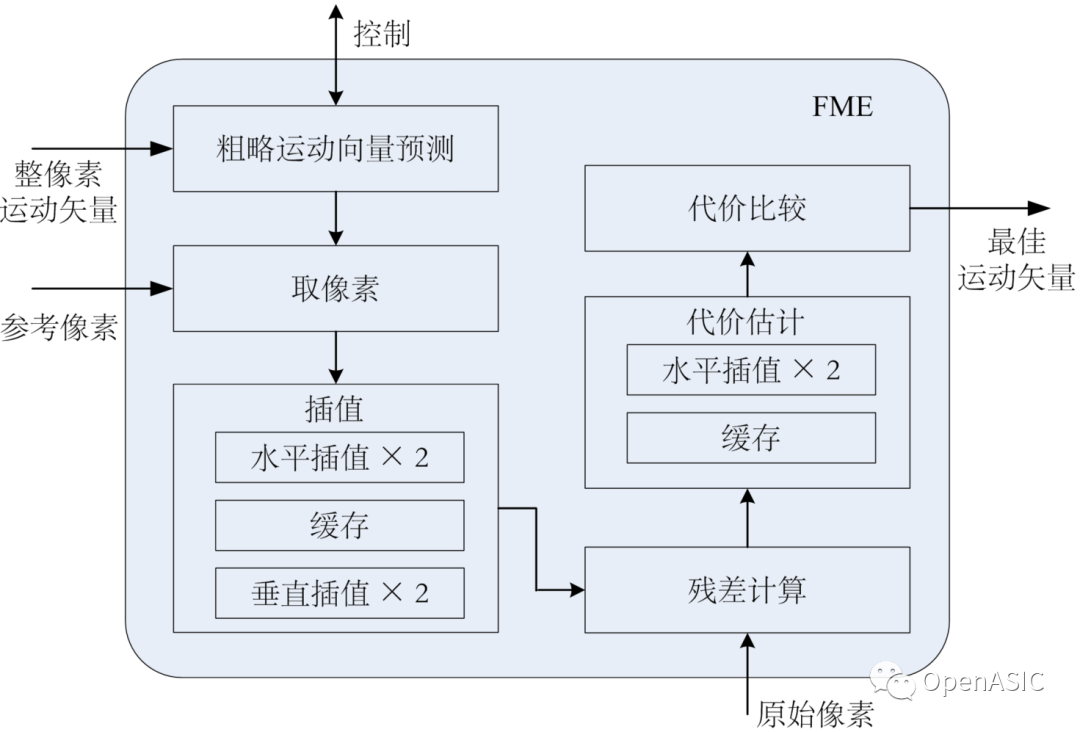

我们提出的分像素运动估计的硬件设计架构如下图7所示。

图7

本文设计的分数运动估计硬件模块只检查2N×2N和N×N的PU块,且基本处理单元为8×8。对于16×16、32×32和64×64大小的PU,其代价由其下的8×8块计算求和得到。

(1) 首先,粗略运动向量预测CMVP模块计算得到MVPA和MVPB,并把当前检查的搜索中心点送到后续的取像素模块。

(2) 取像素模块以当前检查的搜索中心为中心(IMV、MVPA或者MVPB),从参考像素存储器读出16×16大小的参考像素块。

(3) 插值模块依次经过水平插值、转置和垂直插值,将该搜索中心及其附近8个候选点对应的参考像素块(合计9个参考像素块),送到后续的残差计算模块。

(4) 残差计算单元负责将这9个参考像素块与原始像素块做差,得到每个候选点的残差。

(5) 在代价估计单元中,将对残差做SATD操作,并对MVD计算代价,得到9个候选点的代价。

(6) 代价比较单元比较这9个候选点的代价,得到最小代价以及相应的最佳亚像素运动矢量。

性能评估

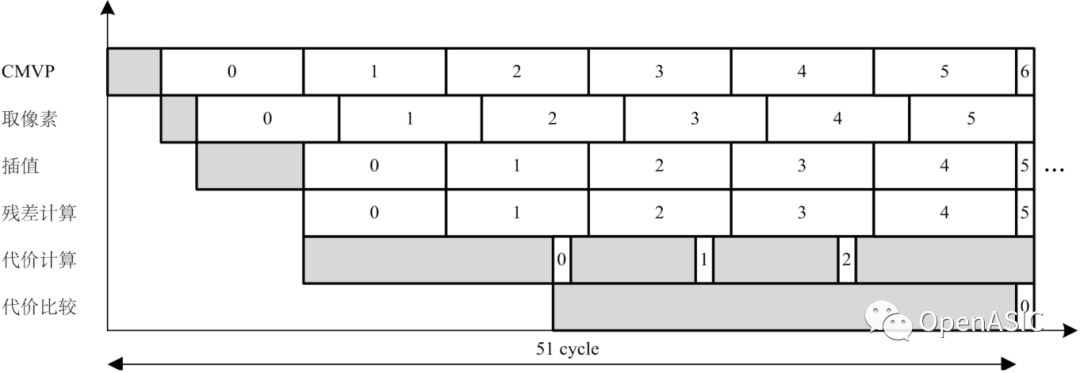

我们提出的分像素运动估计硬件设计的模块时空图如下图8所示,图中的序号代表该模块当前正在处理的8×8块的编号。

图8

观察上图7可以发现,从开始分像素运动估计到输出第一个8×8块的最佳运动矢量需要51个周期,之后每8个周期输出一个8×8块的最佳运动矢量。

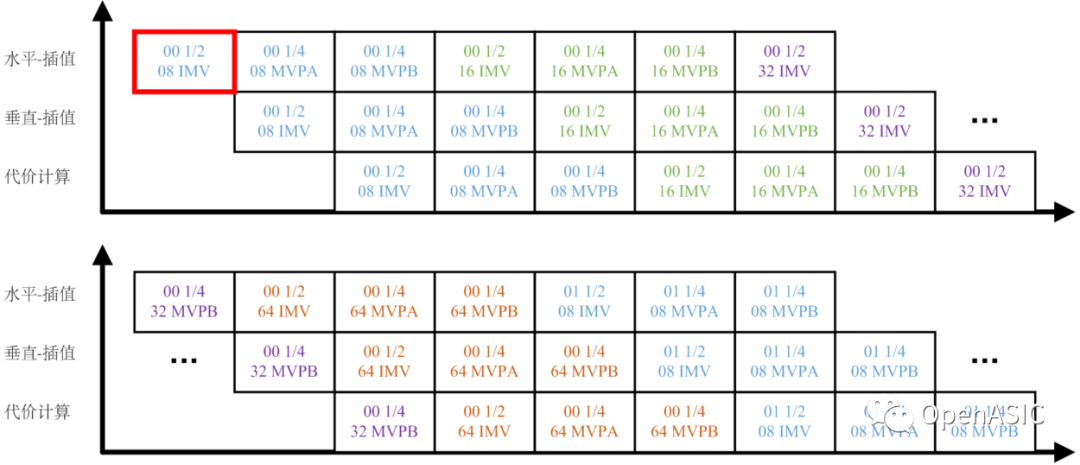

图9

8×8块的计算顺序如上图9所示。以图中红色方框内的8×8块为例:“00”代表该8×8块水平坐标为0,垂直坐标为0;“1/2”代表周边候选点距离搜索的中心点的距离为1/2个像素;“08”表示该块属于8×8大小的PU;“IMV”代表当前搜索的中心点为整像素运动估计得到的整像素最佳运动矢量。

观察上图8可以发现,8×8块的计算顺序为:

(1) 遍历三个候选的搜索中心:IMV、MVPA和MVPB。

(2) 遍历该块所在的各个层次的PU:8×8、16×16、32×32、64x64。

(3) 遍历LCU块内的所有8×8块(zig-zag顺序)。

因此,本文提出的FME硬件设计的总周期数约为:

8×3×4×(64×64)/(8×8)+51 = 6195

本文提出的分像素运动估计模块的工作频率为500MHz,因此其对UHD 4K×2K分辨率视频序列的编码帧率为

500×106/[3840×2160×6195/(64×64)] ≈ 40

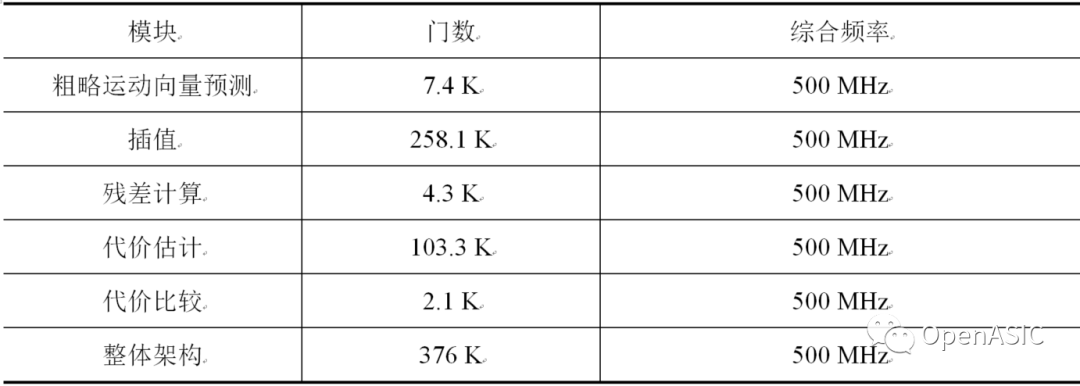

下表3给出了本架构的硬件代价。其中,插值模块占据了68.6%的面积;代价估计模块占据了27.4%的面积;其他模块所占的代价都较小。

表3

我们对所提出的分像素运动估计架构进行了仿真测试,Class A~E的视频序列均仿真通过。此外,我们将综合结果与业界的相关工作进行了比较,如下表4所示。

表4

在分像素运动估计的搜索候选点方面,我们提出的FME架构的搜索点数达到了27个,是这几个工作里面最多的。这是因为本节采用的插值引擎能够同时支持1/2像素和1/4像素的插值,且1/4像素的插值的不需要依赖1/2像素的插值结果,因此整个架构的吞吐率较高。

在硬件门数方面,本文提出的FME架构比He G[3]的工作要更小,这主要是因为我们提出了相对更简单的FME搜索算法,且简化了候选点代价估计的算法。但是,相比较于Lin Y[4]和Kao C[5]的工作,我们提出的FME架构硬件门数要高一些,这是因为我们适用的HEVC编码器的插值方法比H.264编码器的插值方法更加复杂。

参考文献:

[1] Y.-K. Lin,C.-C. Lin, T.-Y. Kuo, and T.-S. Chang. A hardware-efficient H.264/AVCmotion-estimation design for high-definition video [J]. IEEE Transactions onCircuits and Systems I, 2008, 55(6): 1526–1535.

[2] Y. Chen, T.Chen, C. Tsai, S. Tsai and L. Chen. Algorithm and Architecture Design ofPower-Oriented H.264/AVC Baseline Profile Encoder for Portable Devices [J].IEEE Transactions on Circuits and Systems for Video Technology, 2009, 19(8):1118-1128.

[3] G. He, D.Zhou, Y. Li, Z. Chen, T. Zhang and S. Goto. High-Throughput Power-EfficientVLSI Architecture of Fractional Motion Estimation for Ultra-HD HEVC VideoEncoding [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2015, 23(12): 3138-3142.

[4] Y. Lin, C. Lin, T. Kuo and T. Chang.A Hardware-EfficientH.264/AVC Motion-Estimation Design for High-Definition Video[J]. IEEETransactions on Circuits and Systems I, 2008, 55(6): 1526-1535.

[5] Kao C Y, Wu C L, Lin Y L. A high-performance three-enginearchitecture for H. 264/AVC fractional motion estimation[J]. IEEE Transactionson Very Large Scale Integration (VLSI) Systems, 2009, 18(4): 662-666.