视频编解码芯片设计原理----08 环路滤波

本系列主要介绍视频编解码芯片的设计,以HEVC视频编码标准为基础,简要介绍编解码芯片的整体硬件架构设计以及各核心模块的算法优化与硬件流水线设计。

本文将首先介绍环路滤波的基础知识,对H.265/HEVC标准的两种滤波器进行概述。然后分别给出两种滤波器的硬件实现方案,并与已有的硬件实现工作进行对比。

概述

H.265/HEVC的环路滤波技术包含去方块滤波(DBF,De-Blocking Filter)和样点自适应补偿(SAO,SampleAdaptive Offset)两种滤波器,二者可以合称为环路滤波器。DBF先对重建图像进行处理以改善方块效应(blocking effect),处理后的像素经由SAO进一步处理以改善振铃效应。

基于块的混合编码算法会导致块与块之间的不连续性,会影响帧间预测的效率和视觉观感。为了改善这类问题,在反量化后会引入环路滤波来对图像进行进一步处理。经过滤波的重建图像一方面会作为显示输出,另一方面会作为参考帧,继续参与后续帧的运动补偿,因而环路滤波能够有效地提升视频的主客观水平。

01

去方块滤波 (DBF)

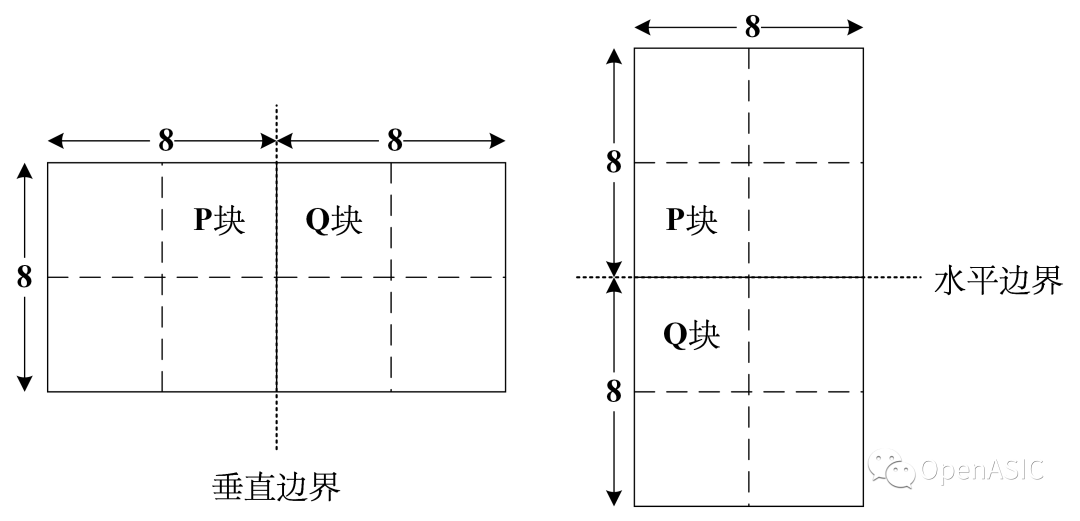

H.265/HEVC去方块滤波器仅对亮度和色度像素的8×8块边界进行滤波,并且滤波边界必须是PU或TU的边界(图像边界除外)。滤波操作以左右(垂直边界)或上下(水平边界)的两个相邻4×4块为单位,这两个4×4块分别称为P块和Q块,如下图1所示。

图1

去方块滤波大致可分为滤波决策和滤波操作。

滤波决策需要根据边界的实际情况,判断是否滤波以及采用何种滤波强度。

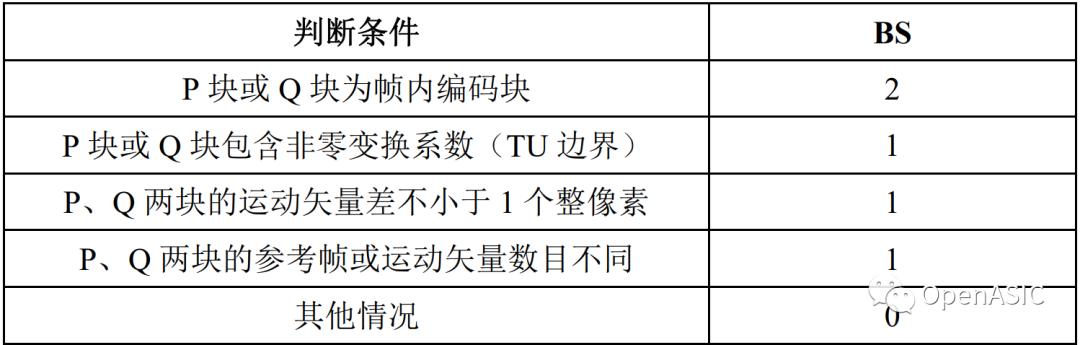

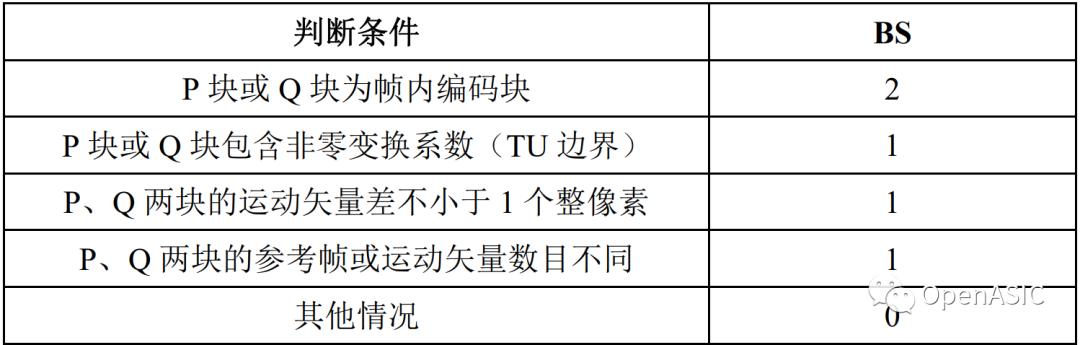

对于待滤波边界,要根据边界两侧像素的特征来判断滤波边界强度(BS,Boundary Strength)。具体判断条件如表1所示。边界强度为0则不进行滤波,而边界强度大于0的时候,还需要进一步判断是否进行滤波,也就是是否开启滤波开关。

表1 边界强度判断条件

由于人眼对于平坦区域中的不连续边界更加敏感,而对于像素本就变化剧烈的非平坦区域,人眼可能无法识别到不连续边界,此时若进行滤波操作,会减弱像素变化的剧烈程度,反而会引入失真。所以只有当区域的变化剧烈程度小于某个阈值时,才开启滤波开关。

在开启滤波开关的情况下,H.265/HEVC中色度分量只有一种滤波模式,但是亮度分量具有强滤波和弱滤波两种模式,因此还需要对亮度分量的滤波强度进行判断,主要也与像素值变化的剧烈程度。当较为平坦的时候,块效应更加明显,需要进行强滤波来实现更大范围和更大幅度的修正;而在相对非平坦的区域则进行弱滤波,防止过度修正导致失真。

滤波操作包含了3个部分:亮度强滤波、亮度弱滤波、色度滤波。亮度强滤波需要用到边界两侧的4个像素,修正范围包括边界两侧各3个像素,并且对P块和Q块像素的处理是对称的。亮度弱滤波中,P块或Q块中的修正范围可能为0~2个像素点,需要根据像素值进行判断,且P块和Q块的判断是相互独立的。色度滤波则较为简单,只要边界强度为2,且滤波开关打开,就对色度分量进行滤波,无需其他判断条件。并且色度滤波只有一种模式,仅修正边界两侧各1个像素点。

滤波操作相关的判断公式及计算公式,可查阅HEVC标准[1]第8.7.2.5节,此不赘述。

样点自适应补偿 (SAO)

样点自适应补偿从像素领域入手降低振铃效应,简单来说就是对解码像素的波谷位置添加正补偿,波峰位置添加负补偿,以此减小像素失真。

SAO首先对每个像素进行类别划分,并计算得到每种类别的补偿值(offset),然后通过计算每种类别的率失真情况得到最优类别,再将最优类别对应的补偿值加到相应的像素点上。SAO包括边界补偿(EO,Edge Offset)和带状补偿(BO,Band Offset)两种模式。

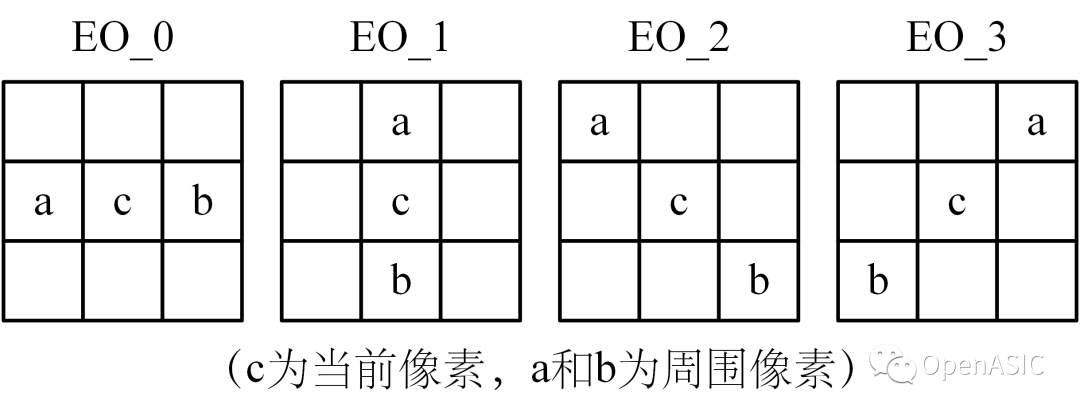

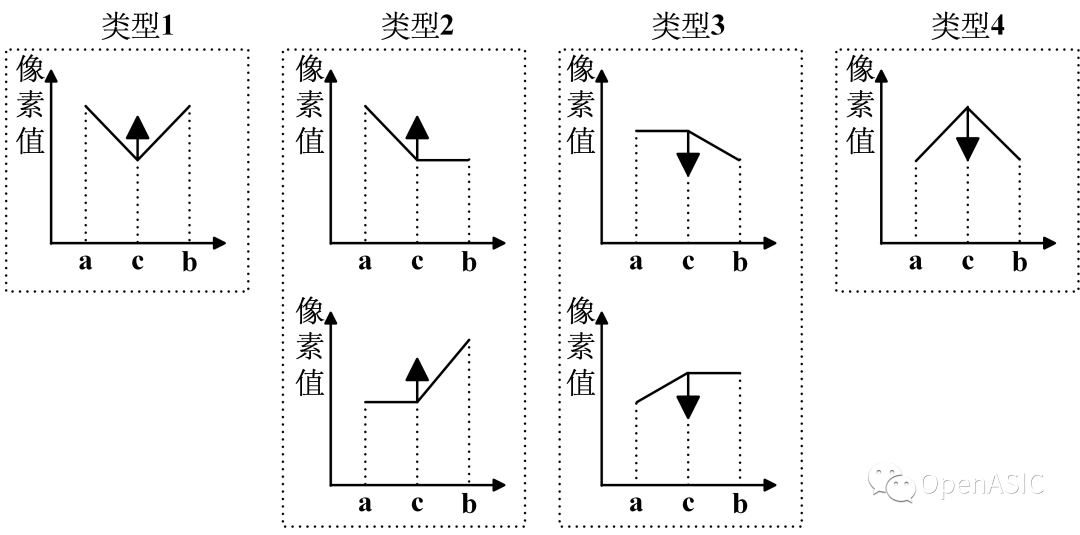

边界补偿模式通过比较当前像素值与相邻像素值的大小对当前像素进行归类,然后对同类像素补偿相同数值。根据当前像素与周围像素选取的不同方向,可分为水平(EO_0)、垂直(EO_1)、斜对角135°(EO_2)和斜对角45°(EO_3)共4种模式,如图2所示。而每种边界补偿模式下,又包括了5种子类型。其中4种子类型如图3所示,其他情况则属于第5种子类型。

图2

图3

带状补偿模式是基于像素值大小进行分类。将像素范围平均分为32个带,编号为0~31。以常规的8比特量化深度为例,其像素值分布在0~255之间,则每个带包含8个像素值。不同的带具有不同的补偿值。带状补偿模式下,以连续4个带为一组(共29组)进行模式判决。之所以为BO模式只选择了4个连续的带作为最优判决结果,是因为一个CTB中像素值的分布区域是有限的,4个连续的带可以覆盖大部分像素点。判决得到最优BO模式后,只需将四条连续带的起始带编号以及相应的4个补偿值作为BO模式信息参与编码,从而大大减低码率需求。

另外,SAO也存在Merge模式。若当前块采用Merge模式,则可复用相邻块(左侧或上方)的SAO参数,从而减小编码SAO参数的复杂度。

DBF VLSI实现

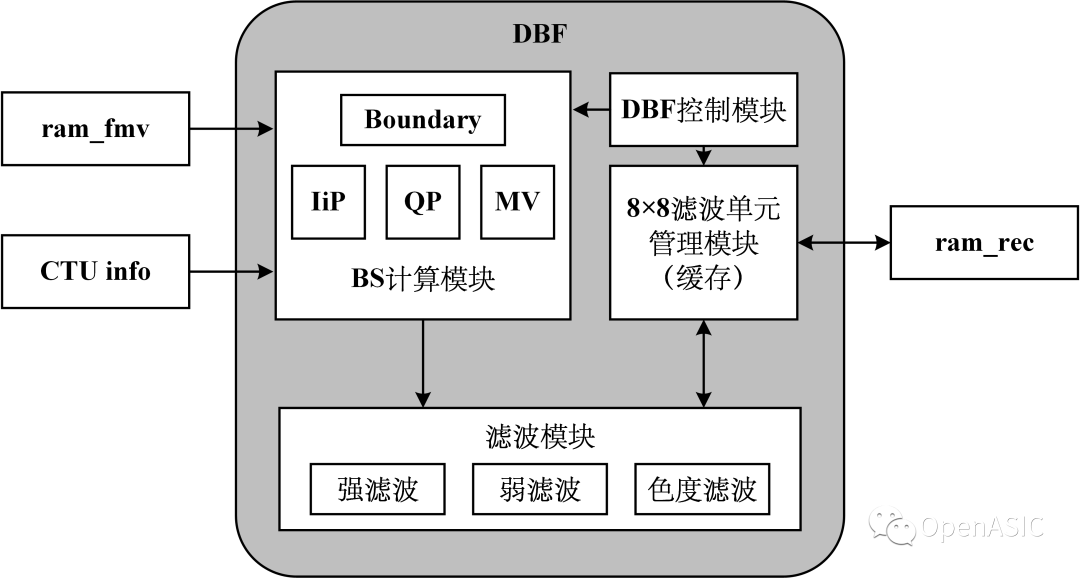

图4是DBF的顶层架构图。

图4

各模块的功能如下:

① DBF控制模块:实现滤波任务的发布,控制滤波单元的遍历、颜色通道以及外部RAM的交互接口,包括ram_fmv(P帧的运动矢量信息)和ram_rec(滤波前的重建像素),取回的数据分别传输给BS 计算模块和8×8 滤波单元管理模块。

② BS计算模块:接收CTU信息后,根据滤波单元的位置和当前边界两侧的编码参数计算边界强度,同时生成滤波判决所需的参数β和。

③ 8×8滤波单元管理模块:负责滤波单元的构建,根据滤波单元的位置信息输出4×8个像素值,其内部是一组缓存。

④ 滤波模块:负责滤波操作,其中包括三类滤波器并行执行,通过判决选择其中之一输出。处理完两个垂直边界后,将输出转置后再次进行相同的操作处理水平边界。

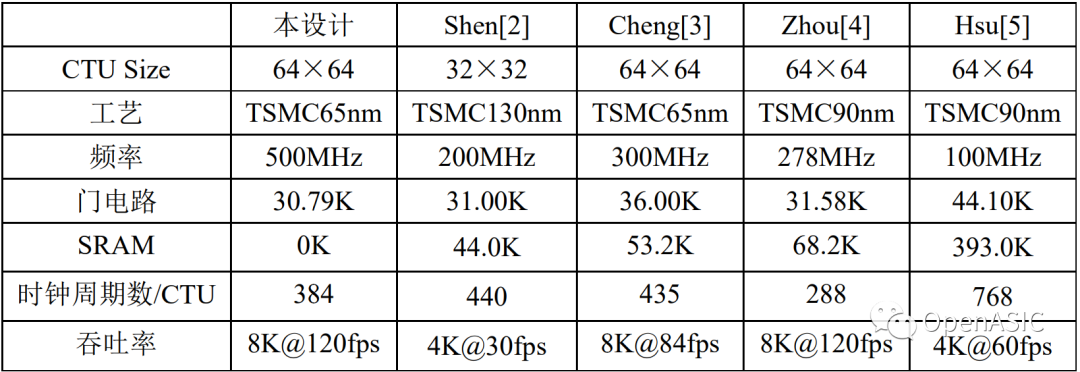

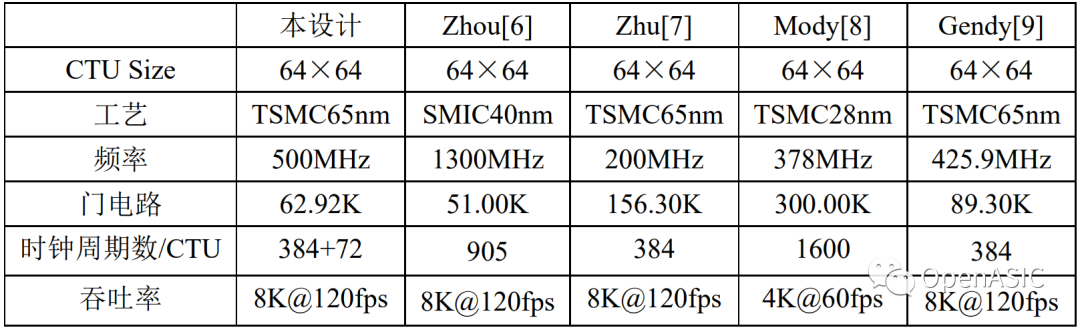

表2将本文实现的结果与已有工作进行了对比。本文提出的基于8×8滤波单元设计,无需使用SRAM存储滤波垂直边界和水平边界的中间像素,大大降低了片上资源代价。最终本文实现的DBF硬件架构,能够满足8K@120fps高吞吐率的视频实时应用。

表2 DBF硬件实现结果对比

SAO VLSI实现

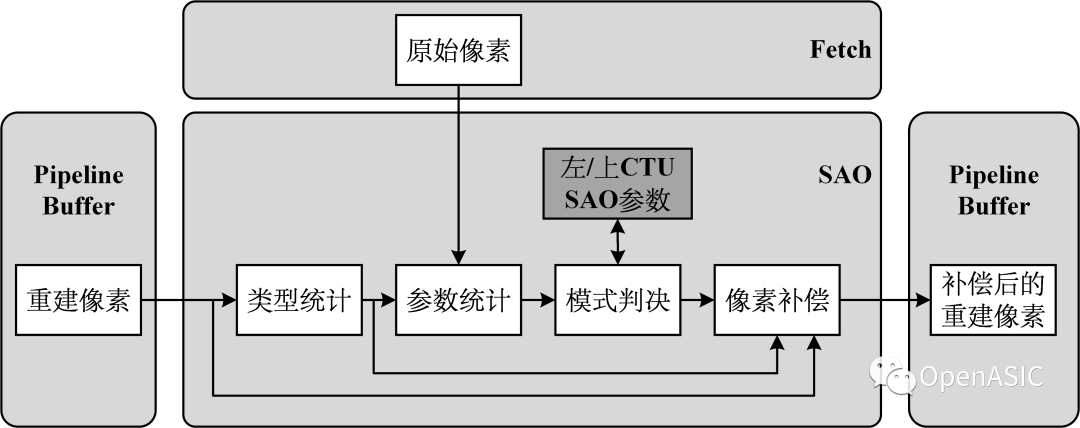

编码端的SAO主要包括三个流程,参数统计、模式判决、像素补偿。参数统计是统计块内部重建像素所属的SAO分类,用于后续的模式判决以及像素补偿;模式判决过程是根据前端统计结果,计算每个类型的补偿值及率失真代价,利用RDO(Rate-Distortion Optimization)公式,选择最优的SAO分类及其补偿值;最后需要根据前端模式判决结果,补偿重建像素,完成输出。而解码端则只需要根据传递的SAO信息对重建像素进行补偿即可。

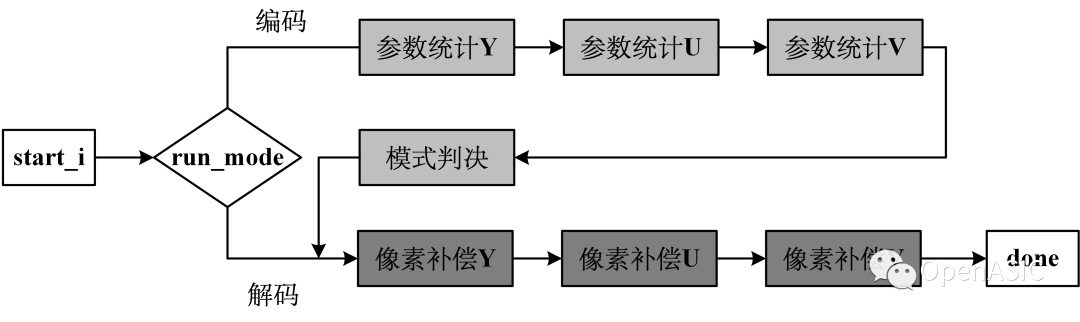

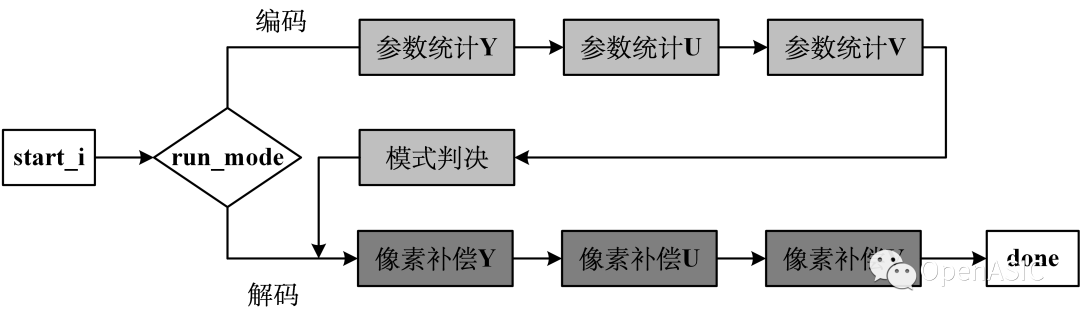

为了适应编码和解码的硬件设计,本节提出可配置的SAO状态机设计,根据需求可配置成编码或者解码方案。图5为状态机转换图及算法流程图,SAO模块收到开始信号start_i后,即执行SAO算法流程,根据配置信号run_mode可以进行编码或者解码的状态机转换。

图5

由于SAO的流程较清晰,且参数统计、模式判决、像素补偿三个过程间具有很强的数据依赖关系,因此本节提出的SAO架构中三个过程顺序执行,通过状态机控制流程,顶层架构如图6所示。

图6

表3和表4对本文工作与其他SAO硬件工作进行了对比。编码端的对比结果显示,本文提出的硬件代价相对较少,吞吐率较高,最高可满足8K@120fps视频实时应用。在解码端SAO相关工作的对比中,本文提出的架构硬件代价相对较低,这得益于高效的SAO分类器。

表3 编码端SAO硬件实现结果对比

表4 解码端SAO硬件实现结果对比

参考文献:

[1] ITU-T Recommendation H.265. Highefficiency video coding[S]. ITU-T, 2013.

[2] Shen W, Shang Q, Shen S, etal. A high-throughput VLSI architecture for deblocking filter in HEVC[C]. 2013IEEE International Symposium on Circuits and Systems (ISCAS2013). IEEE, 2013:673-676.

[3] Cheng W, Fan Y, Lu Y H, etal. A high-throughput HEVC deblocking filter VLSI architecture for 8k× 4kapplication[C]. 2015 IEEE International Symposium on Circuits and Systems(ISCAS). IEEE, 2015: 605-608.

[4] Zhou W, Zhang J, Zhou X, etal. A high-throughput and multi-parallel VLSI architecture for HEVC deblockingfilter[J]. IEEE Transactions on Multimedia, 2016, 18(6): 1034-1047.

[5] Le H H N, Bae J.High-Throughput Parallel Architecture for H. 265/HEVC Deblocking Filter[J]. J.Inf. Sci. Eng., 2014, 30(2): 281-294.

[6] Zhou J, Zhou D, Wang S, etal. A dual-clock VLSI design of H. 265 sample adaptive offset estimation for 8kultra-HD TV encoding[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems, 2016, 25(2): 714-724.

[7] Zhu J, Zhou D, Kimura S, etal. Fast SAO estimation algorithm and its VLSI architecture[C]. 2014 IEEEInternational Conference on Image Processing (ICIP). IEEE, 2014: 1278-1282.

[8] Mody M, Garud H, Nagori S,et al. High throughput VLSI architecture for HEVC SAO encoding for ultra HDTV[C].2014 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2014:2620-2623.

[9] El Gendy S, Shalaby A, SayedM S. Low cost VLSI architecture for sample adaptive offset encoder in HEVC[C].2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). IEEE, 2016:170-175.

[10]Baldev S, Shukla K, Gogoi S,et al. Design and implementation of efficient streaming deblocking and saofilter for hevc decoder[J]. IEEE Transactions on Consumer Electronics, 2018,64(1): 127-135.

[11]Zhu J, Zhou D, He G, et al. Acombined SAO and de-blocking filter architecture for HEVC video decoder[C].2013 IEEE International Conference on Image Processing. IEEE, 2013: 1967-1971.

[12]Kim H M, Ko J G, Park S. Anefficient architecture of in-loop filters for multicore scalable hevc hardwaredecoders[J]. IEEE Transactions on Multimedia, 2017, 20(4): 810-824.