视频编解码芯片设计原理----07 重建环路

本系列主要介绍视频编解码芯片的设计,以HEVC视频编码标准为基础,简要介绍编解码芯片的整体硬件架构设计以及各核心模块的算法优化与硬件流水线设计。

本文给出了HEVC重建环路的相关背景知识,并在此基础上分析了VLSI实现下重建环路所面临的实际问题,并有针对地在模块层次和架构层次对重建环路进行了优化。

概述

重建环路,指的是在重建的过程中,对于当前块的处理必须依赖于前一块的处理结果,导致预测、变换、量化、反量化、反变换和重建的这一系列过程成为了一条首尾相连的环路。变换是将空间域像素形式描述的图像转换至变换域,以变换系数的形式呈现。量化是在变换的基础上对变换系数进一步处理,压缩视频信息量,减小视频码率。

在HEVC 标准中,“重建环路”如下图所示。其中,由预测像素和原始像素相减所得到的残差像素被送往离散余弦变换(DCT)模块和量化(Q)模块,用以得到熵编码(CABAC)模块所需要的变换系数。与此同时,这些变换系数还被送往反量化(IQ)模块和反变换(IDCT)模块用以产生重建后的残差和重建后的像素。

变换与反变换

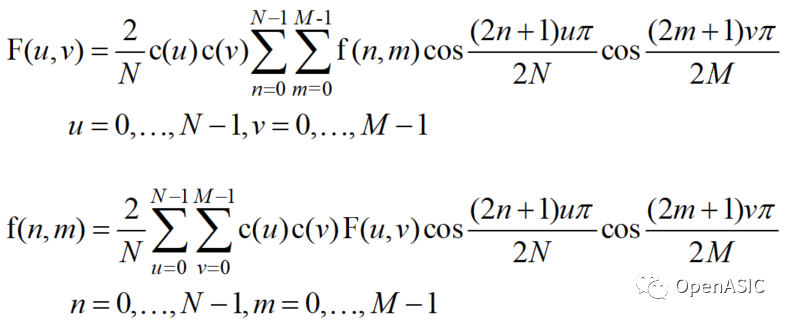

将一维N个实数采样值变换为N个变换域上的变换系数的过程称为一维DCT。DCT变换是一个线性的可逆过程,将N个变换系数重构为N个实数采样值的过程称为逆DCT。二维N×M空间的DCT/IDCT变换定义为如下。

DCT的矩阵系数中包含实数,这种浮点DCT变换会引入浮点乘法计算,并且正变换与逆变换由于精度误差可能产生偏移,因此H.264/AVC、AVS、HEVC等视频编码标准都采用了整数DCT变换。

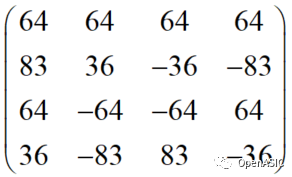

4×4 的DCT 整数变换矩阵:

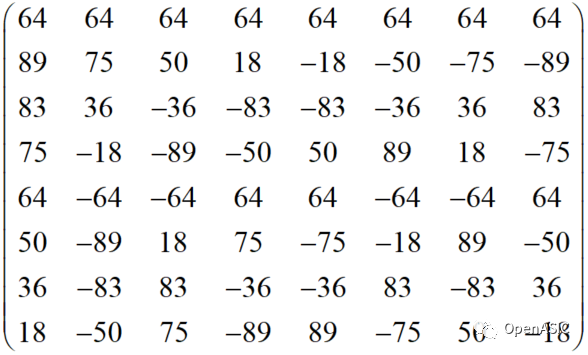

8×8 的DCT 整数变换矩阵:

DCT整数变换是对离散余弦变换的近似,具有可分离性、对称性、递归性等特性。可分离性指二维变换可以通过两次一维变换实现,即先对输入数据做行(列)变换,然后对中间结果做列(行)变换。对称性是指N阶DCT整数变换矩阵中每一行元素具有对称性:偶数行元素左右对称,奇数行元素左右反对称。递归性可以用8×8变换矩阵来举例,可以看到,8×8变换矩阵的第0、2、4、6行的左半部分元素合起来形成的4×4矩阵,即为HEVC中的4×4变换矩阵。

量化与反量化

HEVC中的量化计算过程如下式所示。

反量化计算过程下式所示,其中裁剪的步骤确保了变换系数量化后的值保持16bit位宽。

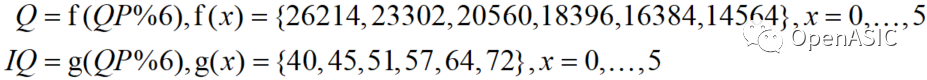

其中参数Q和IQ的定义如下:

其他参数,如coeff代表经过二维整数离散余弦变换后的系数;level代表量化后的系数值;coeffQ代表反量化后的系数值。参数QP代表量化参数;B代表位深;N代表变换尺寸;M=log2(N)。

VLSI实现

设计考量

重建环路在硬件代价上和周期代价上都是HEVC编码器的实现瓶颈。硬件代价直接来源于复杂的预测模式和32×32大小的DCT变换。周期代价则来源于棘手的数据依赖、PU模式的选择和CU、PU、TU块划分的决定,提高对于单个TU/PU的处理速度对于重建环路来说是十分必要的。

变换与反变换

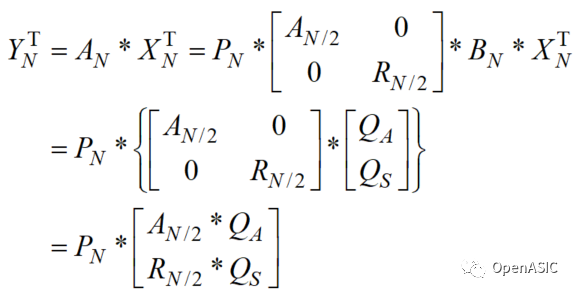

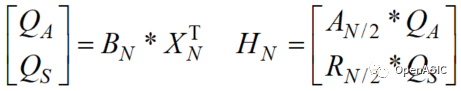

1D-DCT的计算过程可进行如下的分解

其中

因此,N点1D-DCT的硬件实现可以分为四个基本矩阵向量积模块,即BN*XNT模块、AN/2*XN/2T模块、RN/2*XN/2T模块、PN*XNT模块,由基本模块可以实现高性能的1D-DCT变换。

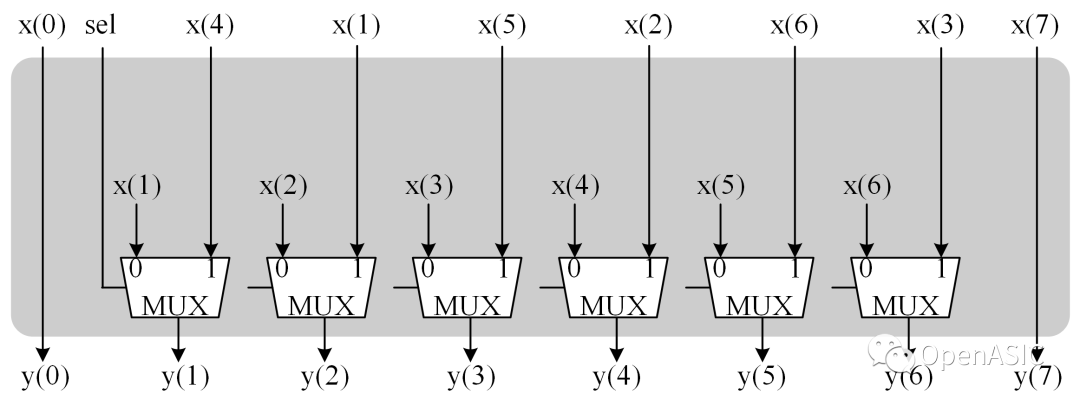

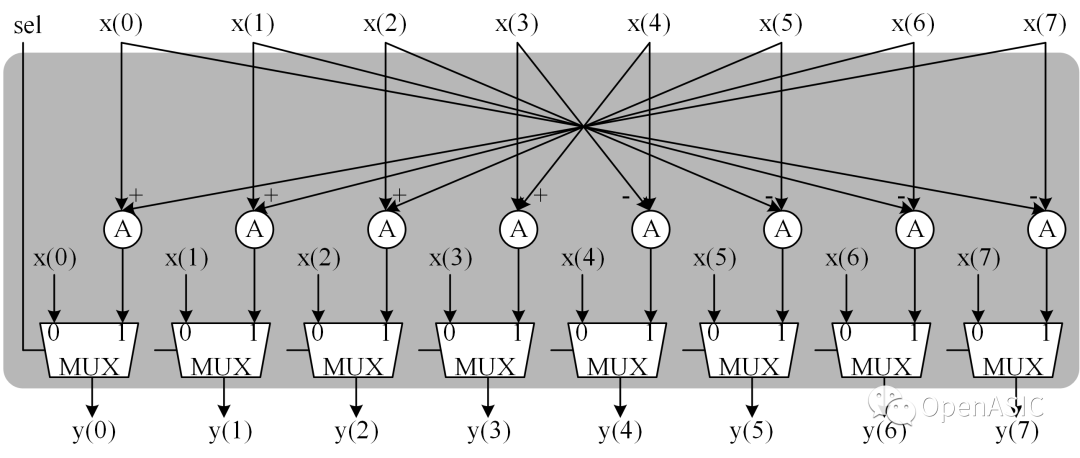

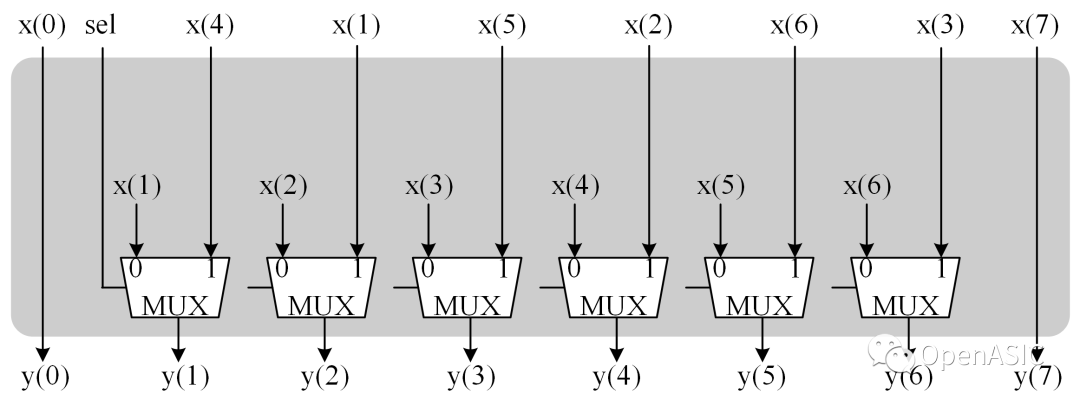

BN*XNT模块的硬件设计以B8*X8T为例,如下图所示。

AN/2*XN/2T模块的硬件设计以A4*X4T为例,如下图所示。

RN/2*XN/2T模块的硬件设计以R4*X4T为例,如下图所示。

PN*XNT模块的硬件设计以P8*X8T为例,如下图所示。

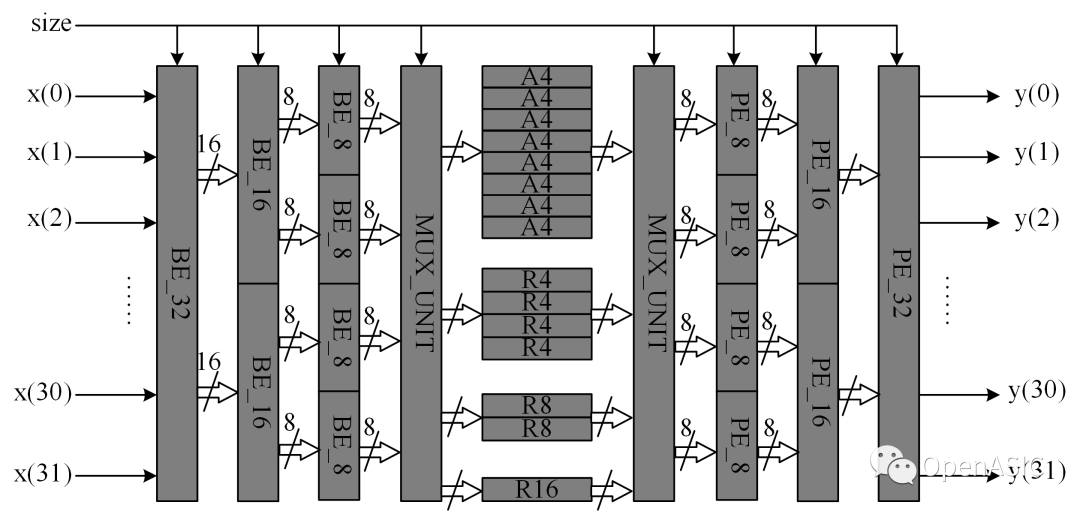

由模块化的设计方法,可以得到同时支持4点、8点、16点、32点DCT变换的硬件结构。适当地调整算法,可以得到一种吞吐率为32点/周期的结构,该变换结构一个周期可以处理8条4点输入向量,4条8点输入向量,2条16点输入向量,1条32点输入向量。下图显示了固定吞吐率为32点每周期的高吞吐率1D-DCT变换硬件结构。

进一步地,由于1D-DCT和1D-IDCT的计算过程相似,均可分三步进行,但运算过程相反。通过一定的算法改进DCT和IDCT可以用一套硬件实现,相比于分立实现,复用结构可以大大减小硬件开销。下图说明了一维DCT模块在正变换和反变换上的复用。

转置存储器

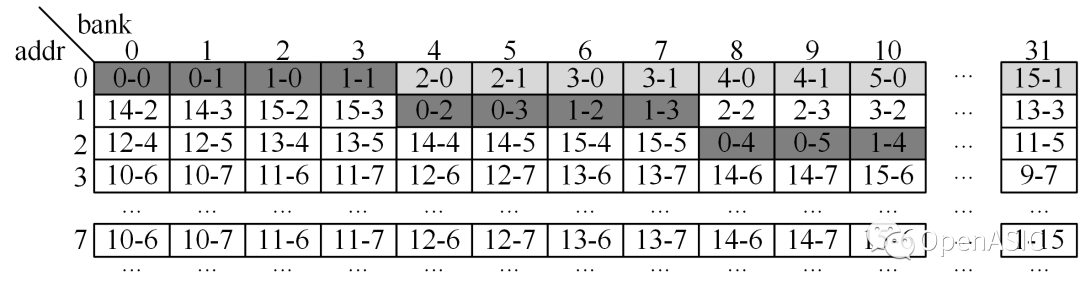

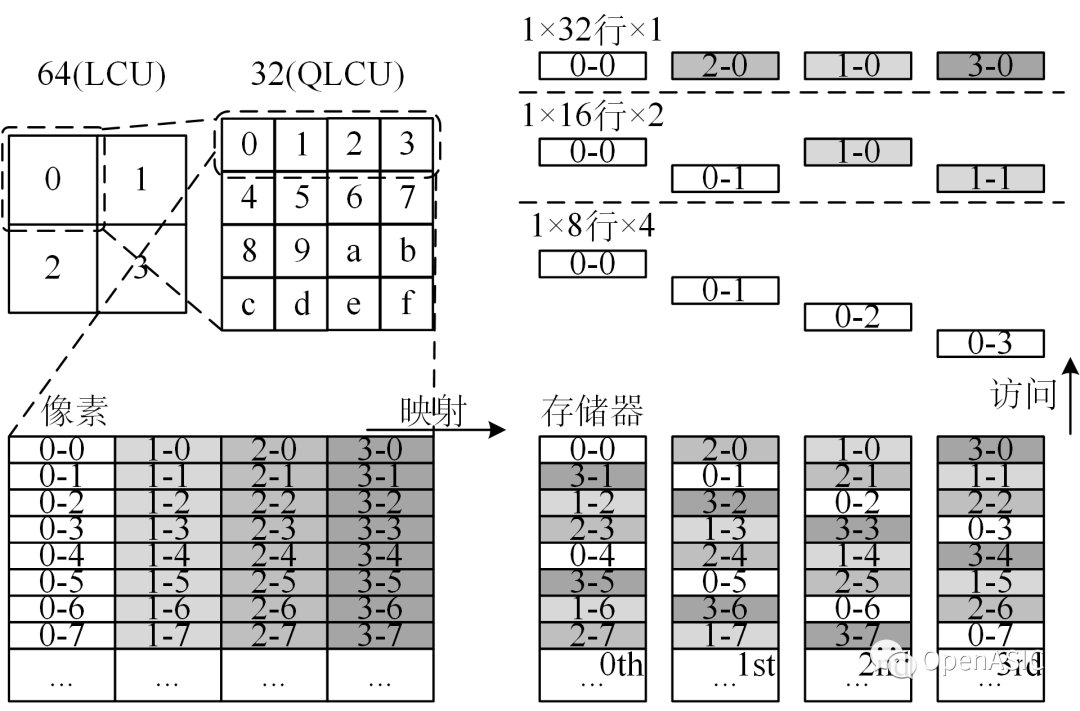

有研究者提出了一种基于单端口SRAM的转置矩阵的地址映射算法[1]。该结构采用一种对角线螺旋式的数据映射方式,可以实现与TU尺寸大小相等的数据吞吐率,如下图所示。

为了能够支持恒定32点每周期的变换/反变换模块,此处对该映射方法进行了扩展。具体地,在处理32×32大小的TU时,仍然按照上述的方法进行映射。在处理16×16大小的TU时,按照下所示的方式映射,映射到每个bank的前7个地址。

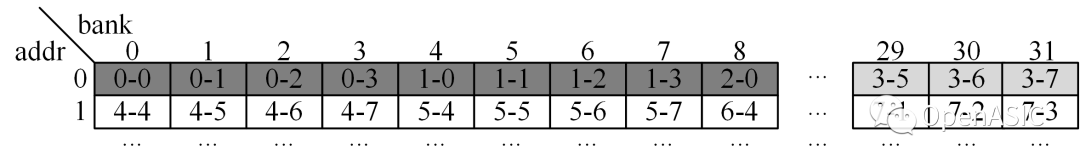

在处理08×08大小的TU时,按照下所示的方式映射,映射到每个bank的前2个地址。

显然地,在这一方式下,无论是32×32块,还是16×16块,亦或8×8块都能够满足32像素每周期的转置速度。

量化和反量化

量化和反量化的主要运算都是乘法、加法和移位,因此HEVC中量化和反量化的计算可以由统一的公式表示,如下所示:

其中,input表示输入系数;q表示量化或反量化的系数;offset表示补偿量;shift表示移位的比特数;

在量化过程中,参数q=f(QP%6),offset根据RDOQ的开关情况进行调整,shift=21+QP/6-M-(B-8)。

在反量化过程中,参数q=g(QP%6)<<(QP/6),offset=1<<(M-2+(B-8)),shift=1<<(M-1+(B-8))。

由计算过程可知,量化、反量化以及量化与反量化硬件复用模块的硬件设计均可分为两部分:参数计算模块和主体运算模块。

下图所示为Q/IQ复用模块的参数计算单元,输出为q,offset,shift三个基本参数。输入为量化步长QP,控制信号CTRL,位深B。

下图所示为Q/IQ复用结构的主体运算单元,量化与反量化可分为乘,加,移位,截位四部分,为了获得更高的性能,可以将主体运算单元分两级流水进行:乘法操作为第一级,加法,移位和截位操作为第二级。

下图所示为N路并行的Q/IQ硬件复用结构,该结构可以支持N路并行的量化、反量化以及量化与反量化复用的操作。

并发存储器

对于预测、去方块化和熵编码模块,由于其处理的基本单元是4×4块,因此,一般采用4×4块的输入输出格式。此处,我们将这种格式称为块格式。对于像素读入,考虑到总线和外部存储器的突发传输特性,像素一般按照光栅顺序读入。此处,我们将这种格式称为行格式。本文提出的并发存储器就是为了以极少的资源代价完成对于上述格式的快速转换。下图将给出并发存储器的具体映射方法。

使用并发存储器,所有左右相邻的4个1×8行都被映射到了不同的Bank中,因此,不管是1×32,1×16还是1×8都能够没有冲突地被访问;特别地,所有上下相邻的2个1×16行和相邻的4个1×8行也被映射到了不同的Bank中,因此,不管是2×16,还是4×8都能够没有冲突地被访问。

架构优化

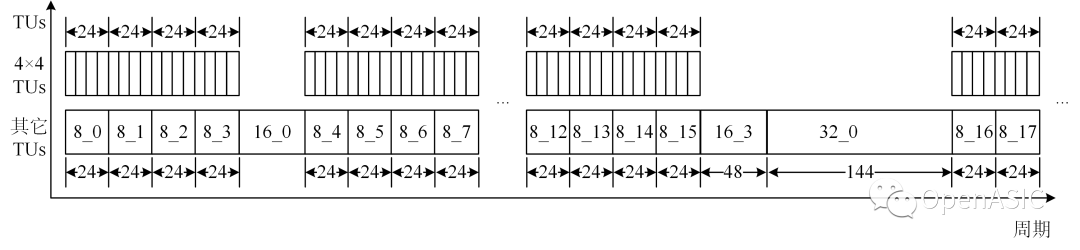

重建环路多数的周期都被消耗在了4×4大小的TU上,但另一方面,4×4块变换的复杂度远比大块变换简单得多。因此,本文对4×4专用通路进行了优化。优化后,重建环路的时空图如下所示。此时,周期数已经减至2880周期。

当重建环路不仅负责PU划分还负责PU模式的决定时,可以选择两种不同的结构。若仍采用全复用的方式,则时空图如下所示,对应的周期数为9816。

值得注意的是,对于同一块不同模式的预测是不存在数据依赖的,因此,上图中对于模式1正向行变换和对于模式0的正向列变换完全可以并行。此时,重建环路的时空图如下图所示。采用这一架构后,重建环路在消耗10092周期的情况下所遍历的模式数高达13个。

资源代价分析

下表给出各个模块所占用的资源代价。由表可知,未复用前,变换/反变换模块的ALUT数目高达108713个,优化后ALUT数目减少为47746个,减少了56.08%的资源消耗;未复用前,量化反量化的ALUT数目为11135,优化后ALUT数目减少为6198个,减少了44.34%的资源消耗。

对于全复用结构,其ALUT代价仅为64K,但在500MHz工作频率下该结构只能够遍历所有划分的5种帧内预测模式;对于半复用结构,其ALUT代价为97K,但在500MHz工作频率下该结构能够遍历所有划分的13种帧内预测模式。在编码器实现时,应根据帧内前预测所提供的模式的准确度、系统所需的编码效果要求和硬件代价要求综合选择合适的复用结构。

参考文献:

[1] S. Shen, W. Shen, Y. Fan and X. Zeng.AUnified 4/8/16/32-Point Integer IDCT Architecture for Multiple Video CodingStandards[A].IEEE International Conference on Multimedia and Expo[C].IEEE,2012:788-793.

模块用以产生重建后的残差和重建后的像素_1652346527094.png)

对于全复用结构,其ALUT代价仅为64K,但在500MHz工作频率下该结构只能够遍历所有划分的5种帧内预测模式;对于半复用结构,其ALUT代价为97K,但在500MHz工作频率下该结构能够遍历所有划分的13种帧内预测模式。在编码器实现时,应根据帧内前预测所提供的模式的准确度、系统所需的编码效果要求和硬件代价要求综合选择合适的复用结构。

对于全复用结构,其ALUT代价仅为64K,但在500MHz工作频率下该结构只能够遍历所有划分的5种帧内预测模式;对于半复用结构,其ALUT代价为97K,但在500MHz工作频率下该结构能够遍历所有划分的13种帧内预测模式。在编码器实现时,应根据帧内前预测所提供的模式的准确度、系统所需的编码效果要求和硬件代价要求综合选择合适的复用结构。