本系列主要介绍视频编解码芯片的设计,以HEVC视频编码标准为基础,简要介绍编解码芯片的整体硬件架构设计以及各核心模块的算法优化与硬件流水线设计。

本章首先介绍了熵编码和熵解码算法的基本原理,并给出其在HEVC标准中的基本流程。然后对熵编码和熵解码的相关子模块进行VLSI设计,得出设计结果与对比。

概述

编码器在经过预测、变换、量化、环路滤波之后产生了大量的待编码数据,这些数据将统一送入熵编码模块进行最后的压缩。熵编码利用信息间的熵冗余,对于信息量大的用长码流表示,信息量小的用短码流表示,进而压缩数据。

编码分类

编码分为定长编码和变长编码。定长编码是将所有的带编码的信息都用同样长短的编码去代表。而变长编码会根据信息熵冗余,频繁出现的用短的编码,不频繁出现的用长的编码。

二进制算法编码

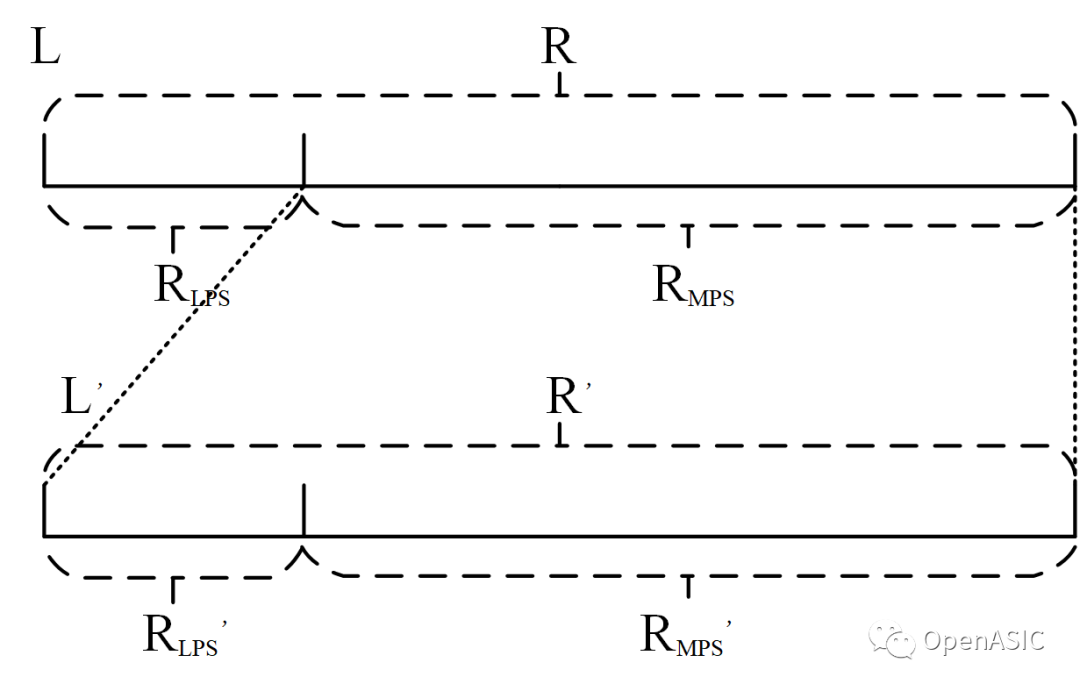

二进制算术编码由算术编码发展而来,但是涉及到的编码对象只有二进制字符“0”和“1”,基本思想是用范围0~1的小数概率区间表示一连串的输入二进制序列。首先统计符号的概率分布,如下图所示。其中MPS表示输入二进制串中出现概率比较大的符号,LPS表示出现概率比较小的符号,R表示区间范围,L表示区间下界,概率统计过程实际上表现为编码区间不断迭代子分。当下一个字符是MPS字符,那么新的区间范围R’使用MPS的区间,其值𝑅′=𝑅×𝑃M𝑃𝑆。

HEVC中的熵编码

HEVC标准中的上下文自适应二进制算术编码(Context-based Adaptive Binary Arithmetic Coding, CABAC)对二进制算术编码做了一些改进,使用了以下技术。

1)自适应二进制算术编码

概率自适应更新直接计算过于复杂,在HEVC标准中将LPS概率区间进行离散化,离散区间为[0.01875,0.5],离散值一共64个,对应状态转换表如下表所示,表格第一行pStateIdx表示当前LPS字符概率量化后的值,第二行transIdxLPS表示输入编码字符为LPS字符时更新后的量化后的概率状态,第三行transIdxMPS表示输入编码字符为MPS字符时更新后的量化后的概率状态。

2)上下文模型

不同种类的输入数据理应有不同的统计特性,因此熵编码引入了上下文的概念。上下文模型将CABAC输入的每个二进制符号进行分类,不同类的数据使用的上下文模型不同,独立进行算术编码的概率更新。

3)乘法优化

区间子分过程涉及到乘法,硬件开销很大,因此在CABAC算法中将这一过程同样优化为查找表,建立了一个64×4的表格,通过查表即可得到已经算好的乘法值。

4)编码字符分类

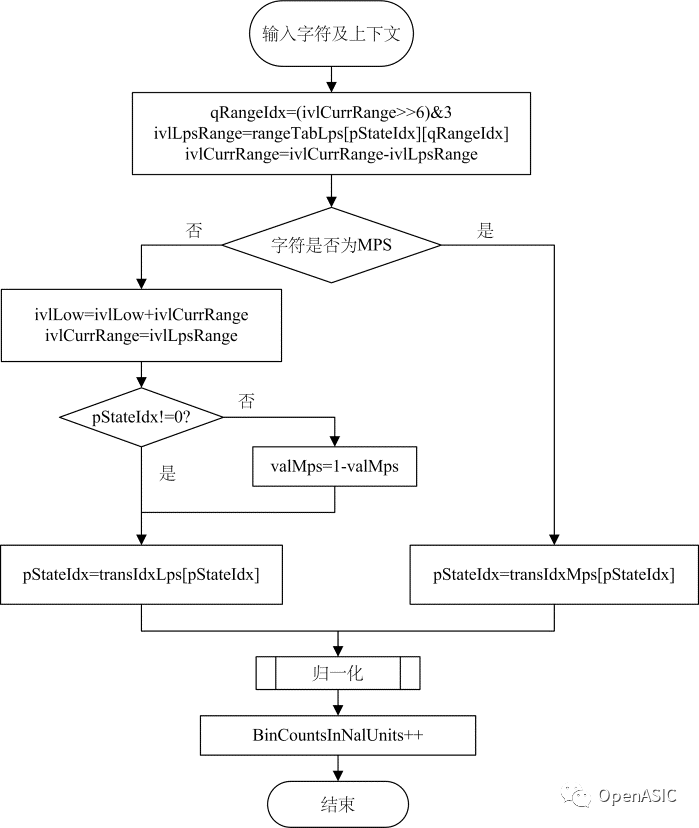

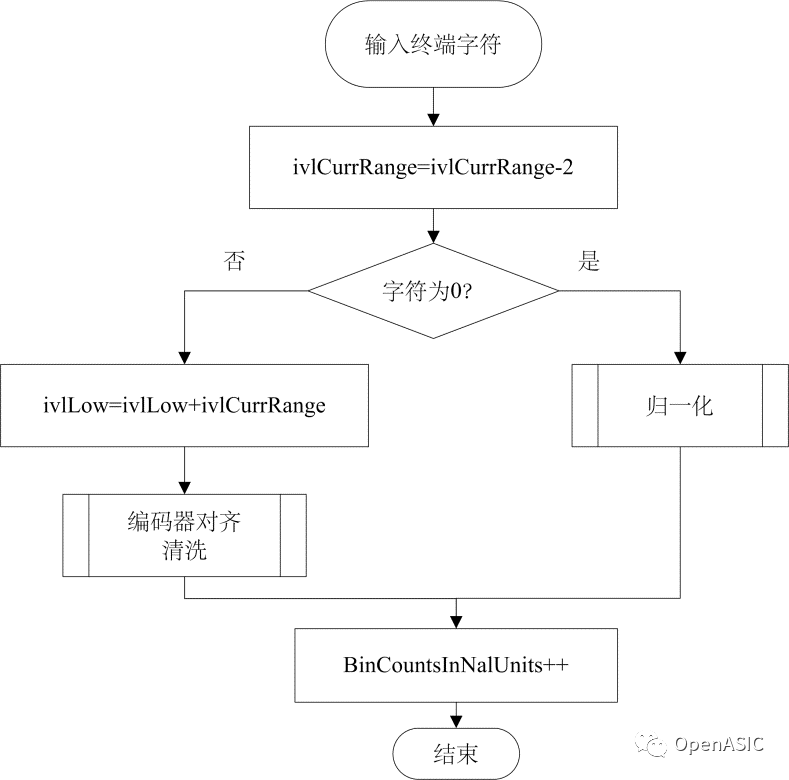

HEVC将编码字符分为三类,第一类是常规模式(Regular Mode)字符,输入不仅包括二进制字符,还需要当前字符的上下文模型,用于根据概率自适应更新编码区间。首先根据当前上下文模型pStateIdx和编码区间ivlCurrRange得到区间范围,接着根据编码字符是否为MPS字符进一步更新下界ivlLow值,最后更新上下文模型,归一化重整区间,如下图1所示。

图1

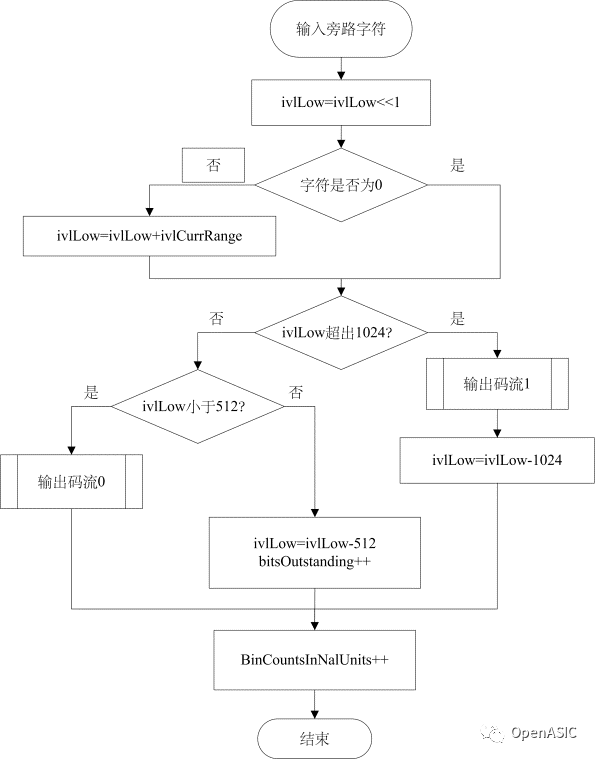

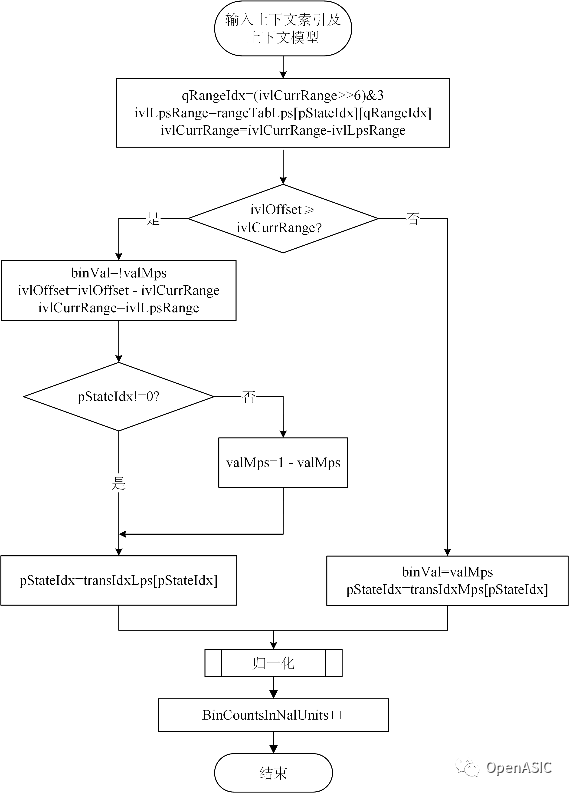

第二类是旁路模式(BypassMode)字符,固定初始LPS概率为0.5,不需要更新上下文,编码流程较为简单,如下图2所示。

图2

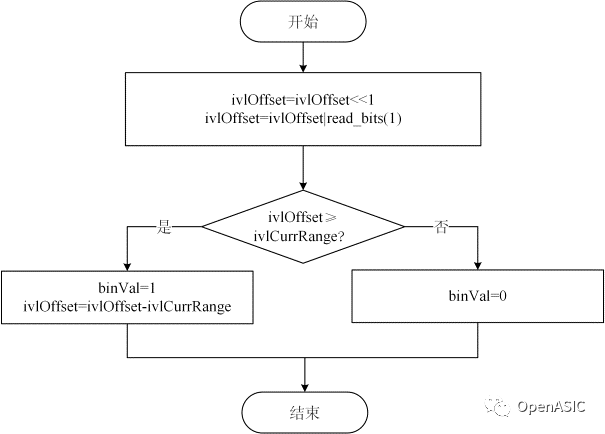

第三类是终端模式(TerminalMode)字符,仅编码结束标志,当帧结束时需要将编码器缓存的码流全部移除并且需要字节对齐,因此这里有个额外的编码器对齐清洗的过程,如下图3所示。

图3

HEVC中的熵解码

编码过程将二进制字符分为旁路模式、常规模式和终端模式三种,熵解码需要有相应的解码引擎与其一一对应。常规解码引擎流程图4如下所示,对比常规模式编码可以发现流程非常相似,区别在于编码不仅需要知道上下文索引还需要输入字符,而解码只需要上下文模型及上下文索引。在初始化过程编码与解码完全相同,接着解码判断ivlOffset值与当前区间范围ivlCurrRange的大小来确定解析出的编码字符是MPS还是LPS。归一化过程会判断是否接着输入1比特码流。

图4

旁路模式解码引擎及终端模式解码引擎流程图如下图5所示,可以看出相对较为简单,且与常规模式解码过程类似,关键判断条件是ivlOffset与ivlCurrRange大小比较。

图5

设计考量

熵编码

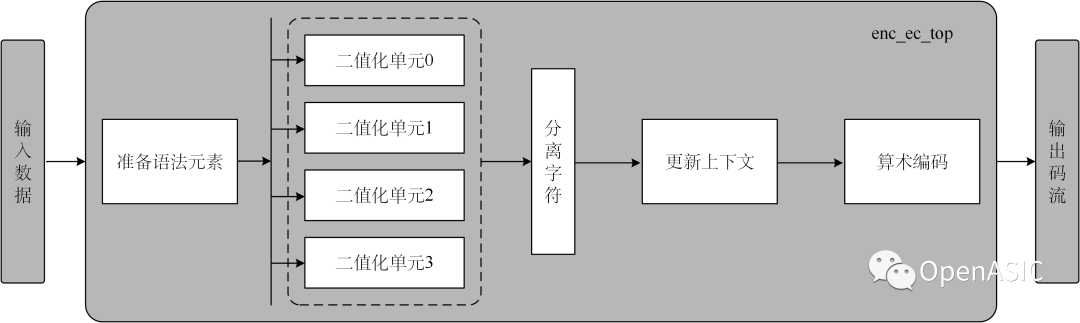

熵编码可分为四部分:“准备语法元素”、“二值化”、“更新上下文”和“算术编码”。“准备语法元素”将熵编码部分输入的整个CTU的数据进行预处理,得到CABAC需要编码的语法元素;“二值化”的作用是将语法元素变成二进制符号;“更新上下文”部分将每一种二进制符号进行概率统计;“算术编码”部分将输入的二进制串进行压缩得到最终的码流。

熵编码主要存在以下设计难点:(1)处理流程复杂,状态机设计复杂。(2)上下文模型更新存在数据依赖,这是一个串行的过程,使用同一上下文的bin需要等上下文更新后才能获得其正确的上下文。(3)算术编码存在数据依赖,算术编码模块由于要自适应迭代编码区间,存在严重的数据依赖。

熵解码

熵解码也可分为四部分:“判断语法元素”、“算术解码”、“更新上下文”和“反二值化”。“判断语法元素”部分按照标准中严格定义的编码顺序同步进行分析,得到当前需要解码出哪一种语法元素。“算术解码”部分先根据判断语法元素给出的上下文模型种类查表得到上下文模型,根据上下文模型里的数据解码引擎解析出当前解码区间范围Range和偏移量Offset,进一步得到解码出的具体二进制字符。“更新上下文”根据解码的二进制字符,上下文模型进行自适应更新以备下一次解码使用。“反二值化”模块将二进制字符还原为语法元素的真实值,至此一个语法元素解析完成。此语法元素会送回“判断语法元素”模块决定下一个语法元素的种类以及上下文模型的类型。

熵解码过程前后存在着严重的数据依赖,主要表现在以下三个方面:(1)“判断语法元素”与“反二值化”的数据依赖。(2)“更新上下文模块”数据更新的依赖。(3)“算术解码”模块区间迭代的数据依赖。

熵编码的VLSI设计

顶层架构

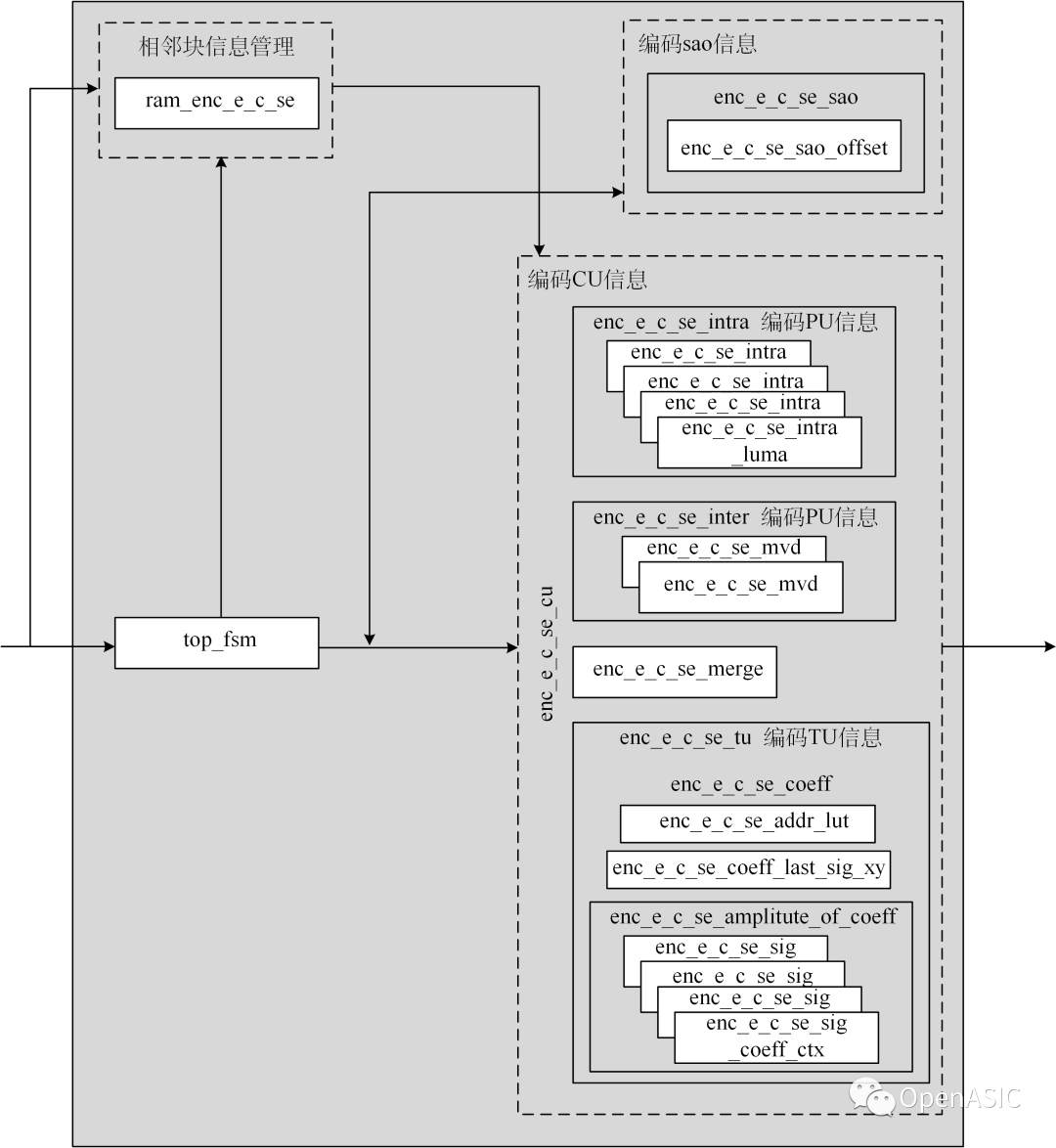

为了提高吞吐率,采用了深度流水的方式进行设计,并尽可能地提高并行度。具体表现为将准备语法元素、二值化、更新上下文和算术编码独立流水,语法元素的准备不依赖后续模块的结果,因此可以深度流水化。对应架构图如下图6所示,分为了五个部分。

图6

准备语法元素模块

图7

top_fsm是“准备语法元素”的顶层状态机,对应了e_c部分最上层的处理逻辑:帧开始初始化->编码SAO信息->根据划分跳转至第一个CU块->循环遍历所有CU->CTU编码结束。

enc_e_c_se_sao模块进行sao信息的编码,输入是62bit的sao数据,输出是一堆需要编码的语法元素,四个一组用于并行。

enc_e_c_se_cu模块编码当前CU的所有信息,因为CU中包含众多数据待处理,这一部分同样使用状态机进行控制,控制逻辑为CU->PU->TU。

二值化模块

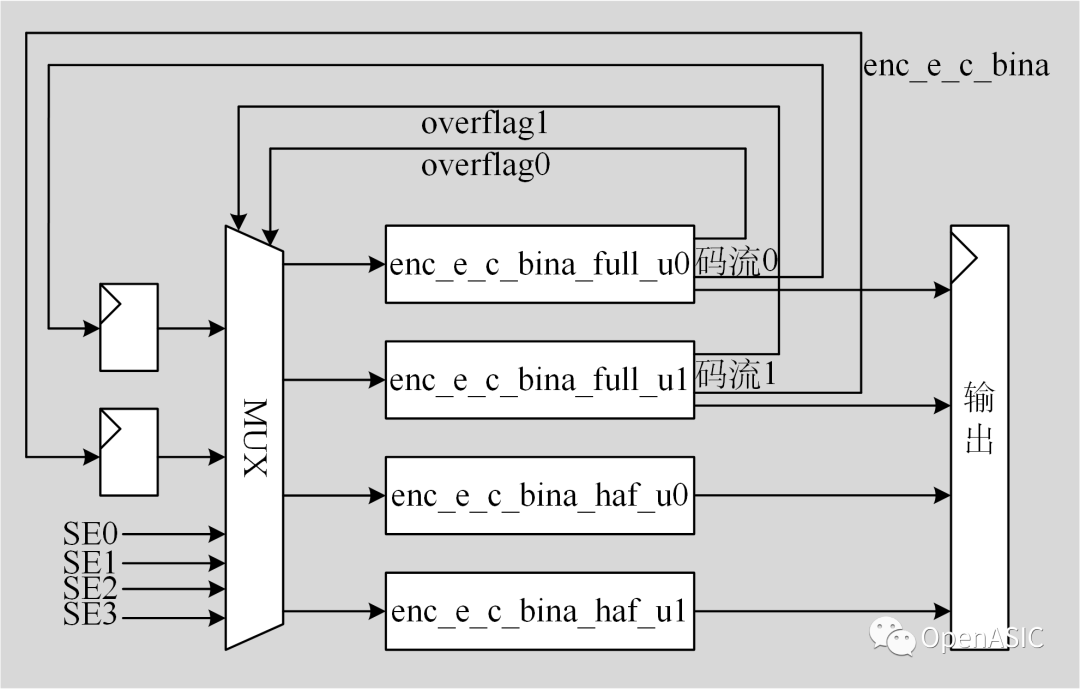

二值化模块将输入的语法元素通过特定的编码方式得到二进制串,同时此模块将决定每个二进制字符最终的上下文模型。考虑到出现连续且大数值的残差系数的场景,判断其超出处理能力后可以先输出前一半,随后输出后一半,将二值化分为两步进行处理,同时“准备语法元素”模块和此模块间使用FIFO进行缓冲,二值化模块结构图8如下所示。

图8

更新上下文模块

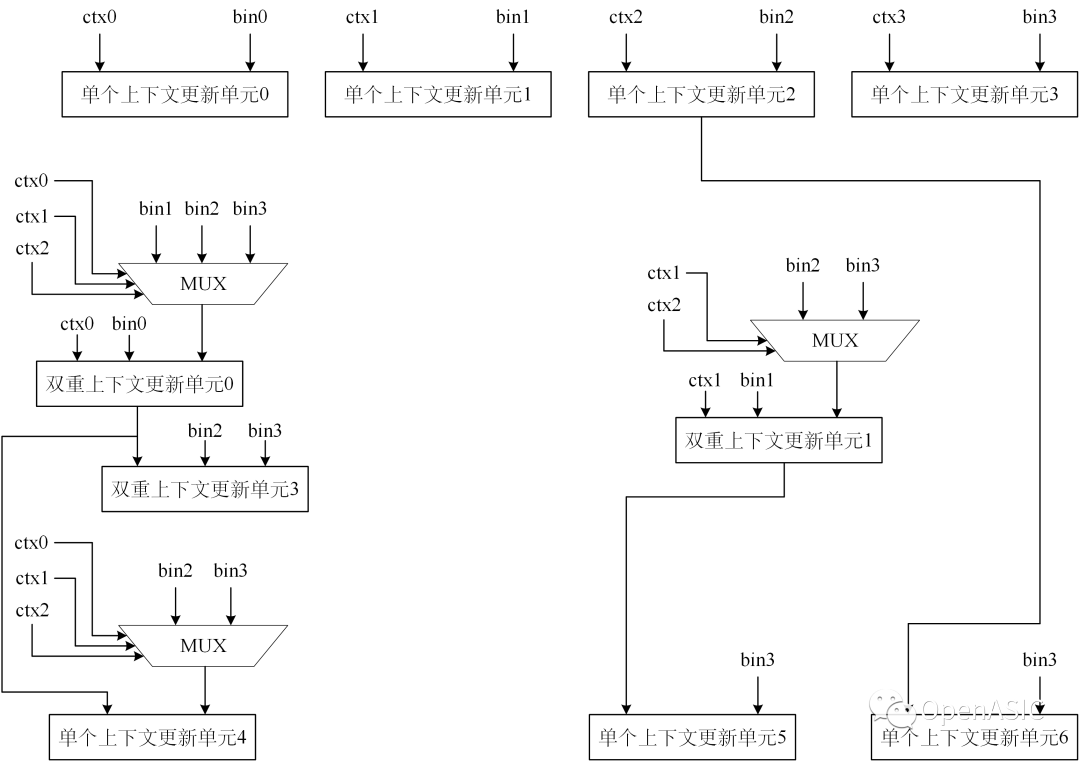

更新上下文模块对不同上下文模型进行独立更新,此模块最多同时更新四个上下文。参考文献[1]的做法,引入双重更新上下文单元,使用双重状态转换表使得更新上下文时关键路径最差情况下不再经过四次更新表格,而是两个双重查找表,能够有效减小关键路径。对应上下文模型更新模块设计如下图9所示,一共使用了七个单个更新上下文单元和三个双重更新上下文单元,输出经选择器选择即可得到准确的输出。

图9

算数编码模块

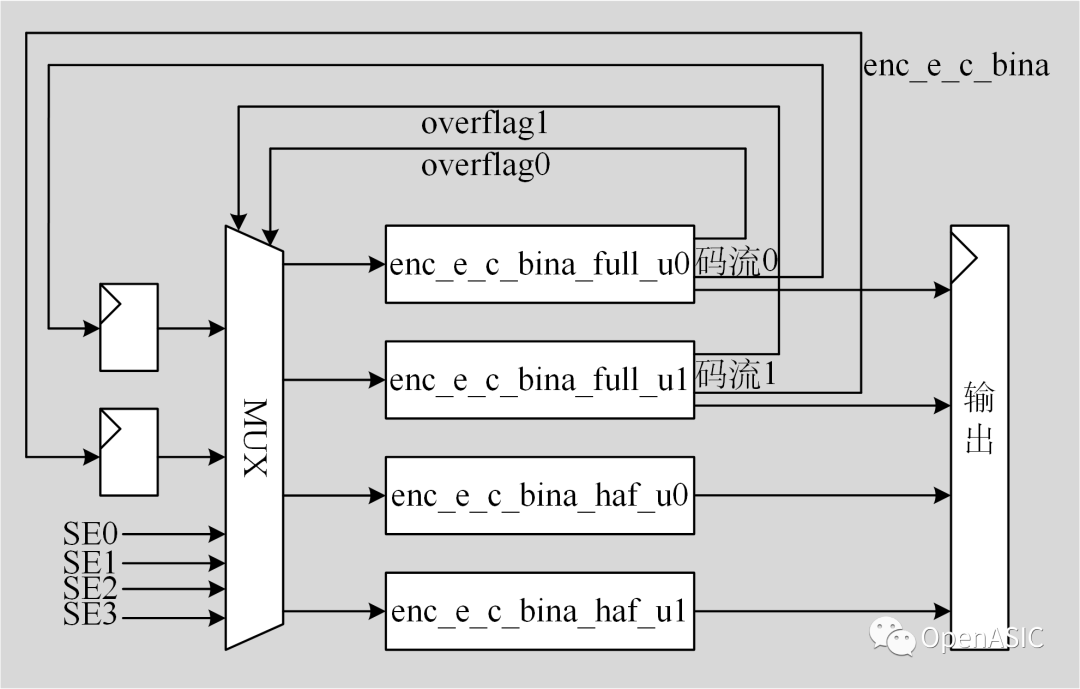

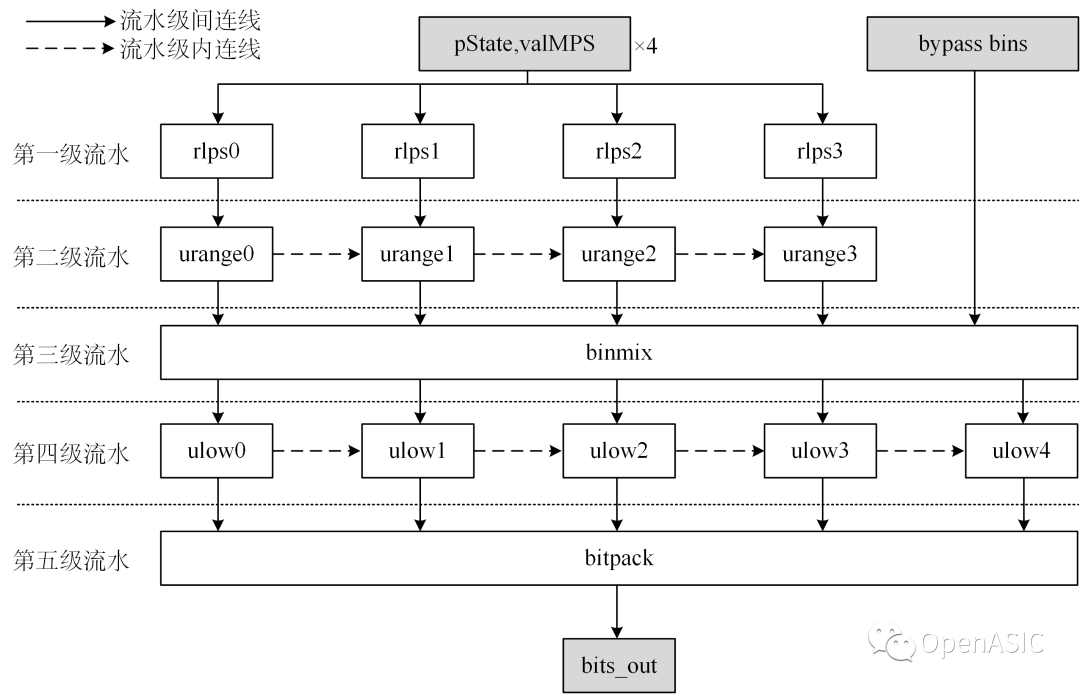

典型的四路并行算术编码结构如下图所示,包含以下几个子模块:enc_e_c_rlps,根据表格rangeTabLps查找乘法结果;enc_e_c_urange,更新当前编码的区间范围;enc_e_c_binmix,由于引入了字符分离的技术,在这里要将所有的编码字符合在一起;enc_e_c_ulow,更新当前编码区间的下界;enc_e_c_ulow_refine,下界与区间范围的整理,调整区间范围至标准范围,输出溢出位;enc_e_c_bitpack,打包前级输出的单bit 码流,每一个byte 输出一次。

图10

性能评估

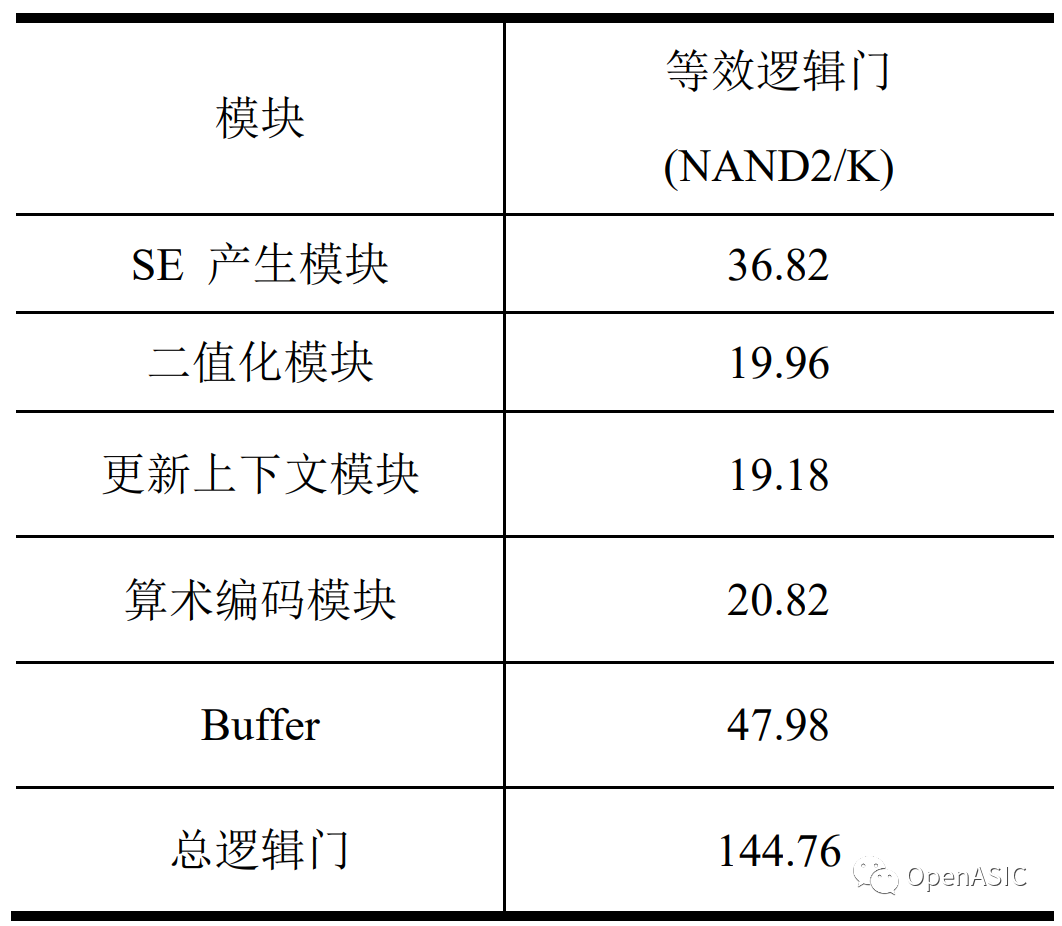

在TSMC65nm 工艺下基于频率500M 对熵编码进行综合得到各主要模块面积如下表1所示。

表1

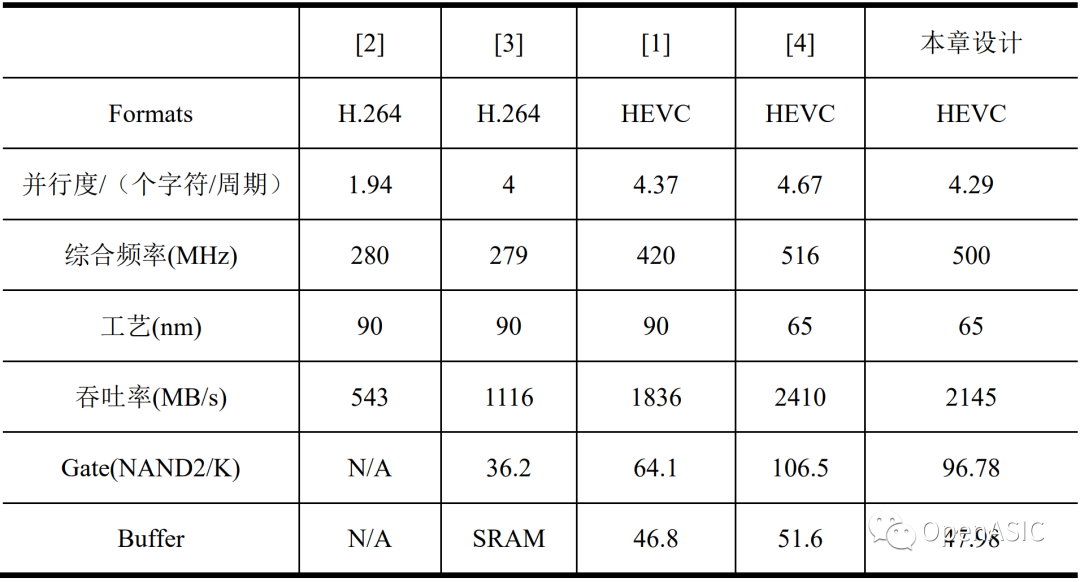

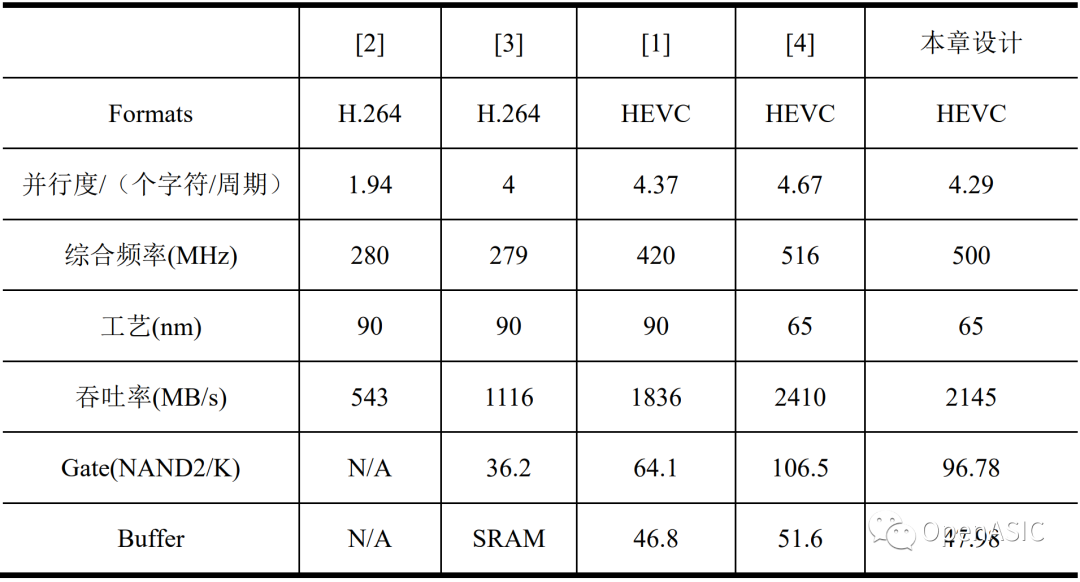

下表将本设计与其他已有研究进行了对比,本设计参考了部分并行技术,实际测试结果每周期能处理4.29个字符,综合频率进一步提升使得吞吐率很高。

表2

熵解码的VLSI设计

下图给出了熵解码模块的架构,由前文分析可知包括“判断语法元素”、“更新上下文”、“算术解码”和“反二值化”模块,此外实际的熵解码码流输入需要满足一定的条件,因此这里需要额外的“码流输入”模块控制输入码流。

表3

输入码流部分

解码过程判断解码是LPS字符还是MPS字符的关键变量是区间范围Range和偏移量Offset值。在解码过程需要不断输入码流,因此输入码流部分需要建立一个码流寄存器,在初始化过程一次移入9比特码流给Offset设置初始值,接着根据算术解码过程产生的是否输入码流以及输入多少比特码流信号输入码流重整Offset。

判断语法元素模块

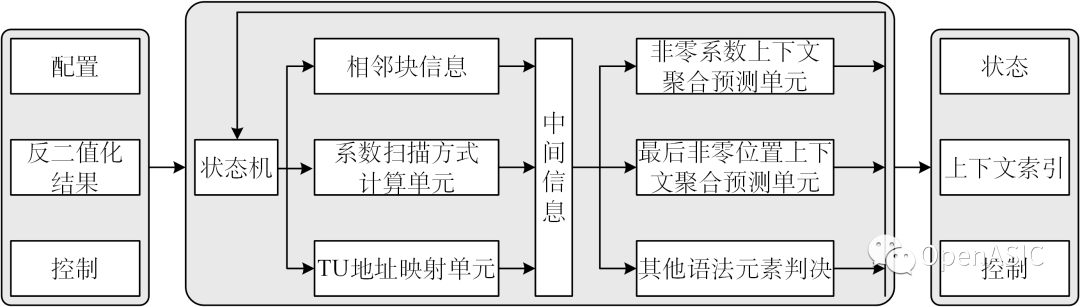

判断语法元素模块的功能是根据已经解析的语法元素,判断接下来的语法元素种类,并且为其各个二进制字符分配上下文索引。因此此模块的输入包括:(1)此码流配置信息,如编码的原视频的分辨率、编码CTU大小等;(2)已解析语法元素;(3)控制信息,控制信息有是否初始化标志、输入码流状态标志两种。为了能够并行处理,判断语法元素部分对语法元素进行了聚合,即一个时钟周期内预测多个语法元素种类并分配上下文索引。此模块的架构如下图11所示。

图11

更新上下文模块

此模块功能较为简单,是用寄存器实现的三读三写存储器,每周期最多同时更新三个上下文,输入为判断语法元素模块生成的上下文索引,以及算术解码引擎解析出的上下文,输出的是更新后的上下文,用于输入算术解码引擎。

算术解码模块

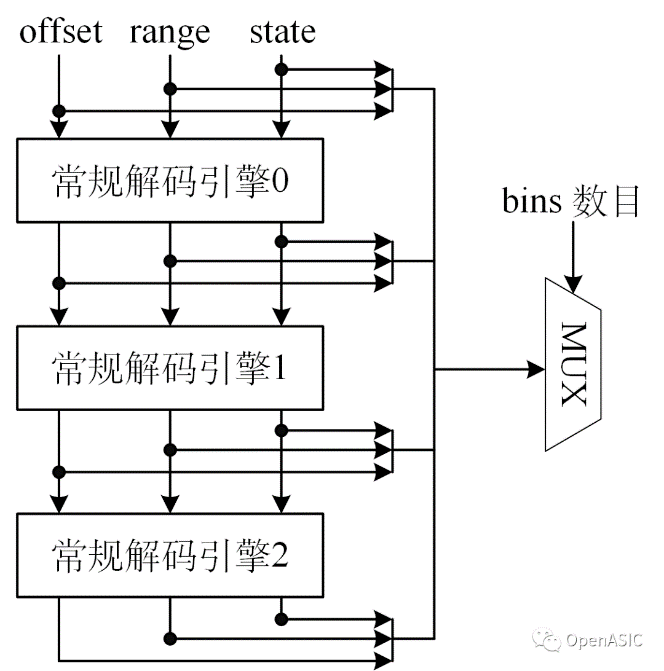

此模块实现常规解码、旁路解码和终端解码三种解码引擎。对于常规解码,由于前级模块均可以每周期处理多个字符,因此这里采用了三个算术解码引擎级联进行并行,如下图12所示,最多同时解码三个常规模式的字符。

图12

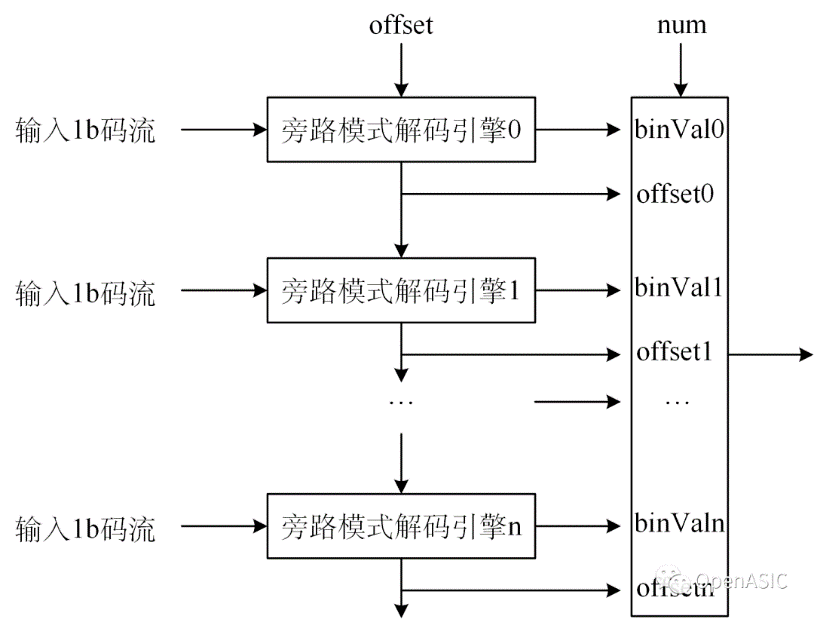

旁路模式字符解码过程相对较为简单,因此可以同时解码多个字符而不会引入新的关键路径。旁路模式解码引擎的并行与常规模式的并行类似,直接进行级联,再由输入需要解码字符数目控制Offset值的更新即输入解码字符即可,架构图如下图13所示。

图13

反二值化模块

反二值化模块需要判断每个语法元素的每个字符是否解析完毕,解析完毕即将接收到的二进制串反二值化还原出具体的语法元素。简单的语法元素由于二值化方式简单,只需要移位加即可还原语法元素,较为复杂且特殊的语法元素利用查找表进行实现。

性能模块

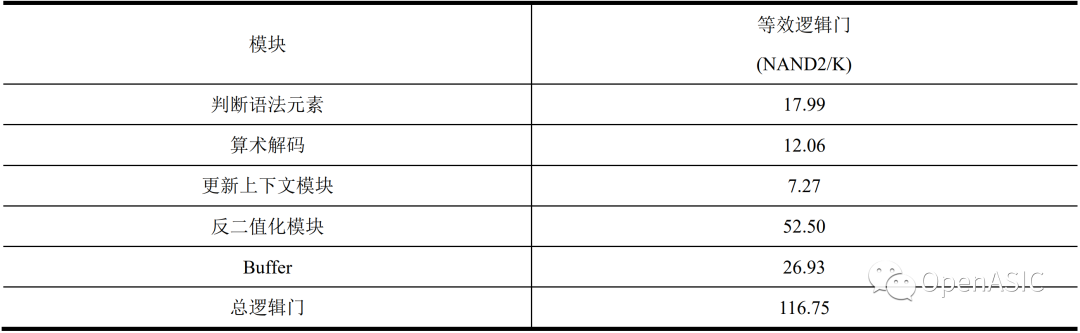

在TSMC65nm工艺下基于频率333M对熵解码做了综合,综合结果如下表4所示。

表4

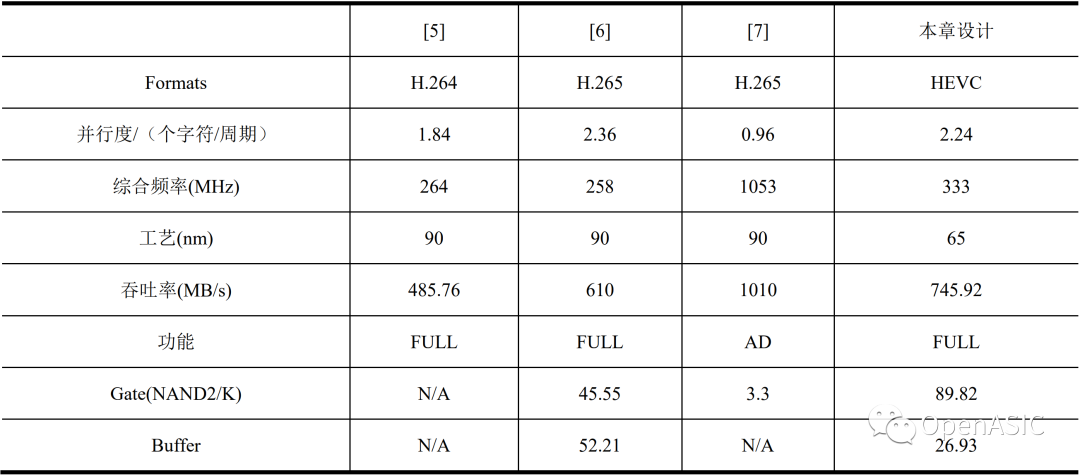

同时将本设计与其他已有设计进行了对比,对比结果如下表所示,本设计能够实现2.24个字符/周期的并行解码。

表5

参考文献:

[1]Zhou D, ZhouJ, Fei W, et al.Ultra-high-throughput VLSI architecture of H. 265/HEVC CABACencoder for UHDTV applications[J].IEEE Transactions on circuits and systems forvideo technology, 2014, 25(3):497-507.

[2] DingL F, Chen W Y, Tsung P K, et al.A 212MPixels/s 4096× 2160p multiviewvideo encoder chip for 3D/quad HDTV applications[A].2009 IEEE InternationalSolid-State Circuits Conference-Digest of Technical Papers[C].IEEE,2009:154-155,155 a.

[3]FeiW, Zhou D, Goto S.A 1 Gbin/s CABAC encoder forH. 264/AVC[A].2011 19th European Signal Processing Conference[C].IEEE,2011:1524-1528.

[4] LiW, Yin X, Zeng X, et al.A VLSI Implement of CABAC Encoder for H.265/HEVC[A].2018 14th IEEE International Conference on Solid-State andIntegrated Circuit Technology (ICSICT)[C].IEEE, 2018:1-3.

[5]LiaoY H, Li G L, Chang T S.A highly efficient VLSI architecture for H. 264/AVClevel 5.1 CABAC decoder[J].IEEE transactions on circuits and systems for videotechnology, 2011, 22(2):272-281.

[6] ZhaoY, Zhou J, Zhou D, et al.A 610 Mbin/s CABACdecoder for H. 265/HEVC level 6.1 applications[A].2014 IEEE InternationalConference on Image Processing (ICIP)[C].IEEE, 2014:1268-1272.

[7] ZhouJ, Zhou D, Zhang S, et al.A Variable-Clock-Cycle-Path VLSI Design of BinaryArithmetic Decoder for H. 265/HEVC[J].IEEE Transactions on Circuits and Systemsfor Video Technology, 2016, 28(2):556-560.